ISSN: 1682-3915

© Medwell Journals, 2016

# Hard Switching Versus Soft Switching-Case Study on Positive Output Elementary Super Lift Luo Converter

<sup>1</sup>Shibu J.V. Bright, <sup>2</sup>Hithu Anand and <sup>3</sup>S. Ramkumar <sup>1</sup>Department of EEE, Maria College of Engineering and Technology, Attoor, Tamil Nadu, India <sup>2</sup>Department of EEE, SSN College of Engineering, Chennai, Tamil Nadu, India <sup>3</sup>Department of EEE, Sri Krishna College of Engineering and Technology, Coimbatore, Tamil Nadu, India

Abstract: Luo converter is a developed converter which transfers the voltage based on lifting and achieves a high voltage gain in geometric progressive law. Researchers show more interest on control of Luo family converters while their procedural steps involved in design is not detailed to gratify the beginner in the field. In regulated power supply applications, Luo converters are more preferred if they operated in soft switching mode. Soft switching techniques like Zero Voltage Switching (ZVS) has reduced switching losses and hence improved efficiency and life of power semiconductor switches. This study takes up and provides complete design of Positive Output Elementary Super Lift Luo Converter (POESLLC) for the 25.92 W rating, firstly. Secondly, the performance evaluation of ZVS based POESLLC over hard switched POESLLC is aimed. Proportional Integral (PI) control of POESLLC for hard switched and ZVS switching are compared in MATLAB-simulink platform.

Key words: Luo converter, POESLLC, soft switching, voltage lift, ZVS

## INTRODUCTION

Switched-mode dc-to-dc converters are used to convert the unregulated dc input into a controlled dc output at a desired voltage level. dc-dc converters are widely used for traction drives in electric automobiles, trolley cars, marine hoists, forklift trucks, mine haulers, communication devices etc. Switching converters have been in existence since 1950 s for the applications varying their ranges from power supplies to DC motor drives. Switching power supplies demand higher energy efficiency, a higher power packing density and reduced Electromagnetic Interference (EMI). To consider the ever increasing requirements for smaller size, lighter weight, higher voltage transfer gain and higher efficiency power supplies, switched-mode power conversion technologies have evolved from basic Pulse-Width-Modulated (PWM) converters to resonant converters, quasi-resonant converters (QRCs), Multi-Resonant Converters (MRCs) converters etc (Luo and Hong, 2006; Luo and Fang, 2004). Even though the performance parameters of the converter can only be improved by control techniques, higher voltage transfer gain is inherent characteristics of topology of the converter. A higher voltage transfer ratio

with reduced ripple content is achieved in Luo converter in simple structure (Luo and Ye, 2003a, b). Luo converter is a developed converter, introduced by Fang Lin Luo in 1977. In Positive Output Elementary Super Lift Luo Converter (POESLLC), the voltage increases in geometric progression (Luo and Ye, 2003).

For the simplicity of analysis, converters are operated under continuous conduction mode. However PWM POESLLC converter under discontinuous conduction mode, a detailed analysis has been presented (Zhu and Luo, 2004). Increasing switching frequency or size of energy storing elements will make the converter in continuous conduction mode and reduced ripple content at the output. With increased frequency hard switching operation, semiconductor switches experience high switching losses (Mohan et al., 2006). This will restrict the converters from operating at a higher frequency and hence, the mission towards size/weight reduction and performance improvement is impeded. Soft switching technique has improved the switching frequency of the same converter with reduced switching losses (Marian and Czarkowski, 2011). The design procedure for very high frequency resonant boost converters has been given (Burkhart et al., 2013). The POESLLC is a new series of

dc-to-dc converters having high voltage transfer gain, high power density, high efficiency, reduced ripple voltage and current. These converters effectively enhance the voltage gain in power-law terms (Luo and Ye, 2003ab).

Having reviewed the literature exhaustively it is understood that the progressive converters like POESLLC has not been treated well to enable the researchers to commence their study. The basic operation, performance indices (voltage ripple etc.,) application specific designs etc. may enlighten their study further. This study provides a detailed design procedure for POESLLC after detailing the mode diagrams based working. The design is followed by a development of Proportional-Integral (PI) controller based POESLLC system implemented in MATLAB-Simulink. The performance difference between ZVS and hard switched systems are well demonstrated using the results such as ripple voltage and transient start-up etc.

#### MATERIALS AND METHODS

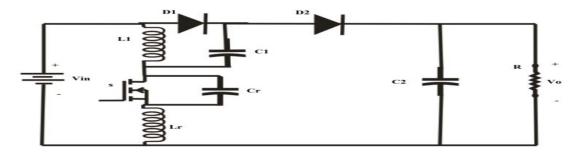

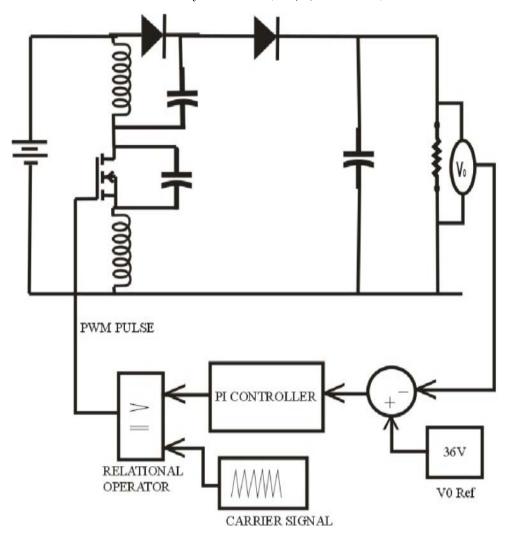

**Proposed PI controller based system:** The proposed PI controller based system consists of a resonant switch added in the converter as shown in Fig. 1 so the working is under soft switching. The resonant inductor  $L_r$  and  $C_r$  form a series resonant circuit. When observing from switch terminal due to resonance the voltage across the circuit including switch, resonant circuit and source will swing to obtain a zero crossing instant.

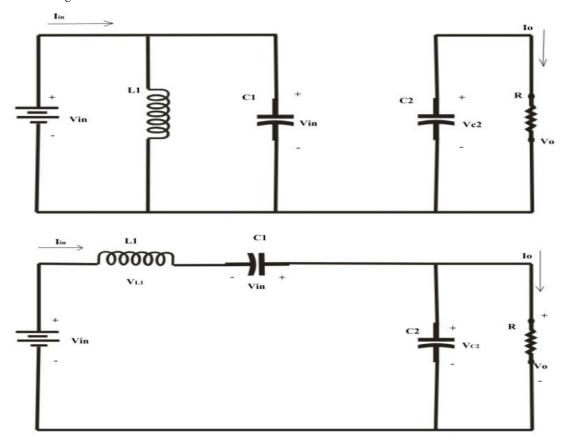

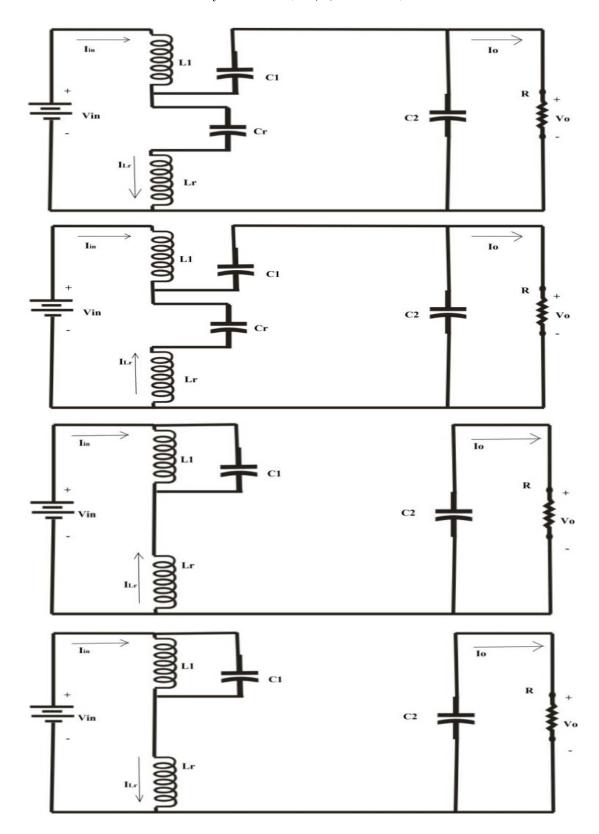

POESLLC under PWM switching: The Pulse-With-Modulation (PWM) is the simplest triggering method for attaining different voltage levels for different duty ratio. It has frequency limitations in the converters due to increased switching losses. The abrupt discharges of energy stored in semiconductor switches are the cause of this limitation. A small signal energy factor and mathematical model for dc-dc converter is given (Luo and Ye, 2007). The two basic modes of operation of the converter under PWM operation is shown in Fig. 2ab. Super-lift luo-converters with capacitor voltage drop is given (Luo, 2008).

The voltage lift technique opens a good way to improve circuit characteristics (Luo, 1999). After long-term research this technique has been successfully applied for dc-to-dc converters. Positive output Luo converters are a host of relatively recent dc-to-dc step-up (boost) converters which were developed from prototypes using voltage lift technique by Luo. In simple structure the Luo converters will give an output voltage with fewer ripples. The other similar category of Luo converters are called Negative Output Super Lift Luo Converters (NOSLLCs).

Its output voltage is negative with respect to input voltage. NOSLLC and reduced-order sliding mode controller plus proportional double integral controller for negative output elementary super-lift Luo-converter are given (Luo and Ye, 2003ab; Kumar and Jeevananthan, 2010, 2013).

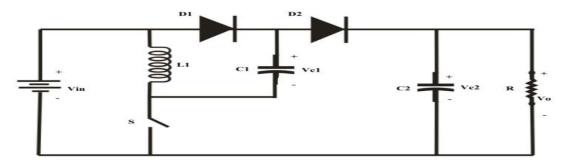

The POESLLC consists of dc supply voltage  $V_{\rm in}$  capacitors  $C_1$  and  $C_2$  inductor  $L_1$ , power switch (n-channel MOSFET) S, freewheeling diodes D1 and D2 and load resistance R is shown in Fig. 2. When the switch S is closed, voltage across the capacitor  $C_1$  is charged to  $V_{\rm in}$ . The current  $i_{\rm L1}$  flowing through inductor  $L_1$  increases with voltage  $V_{\rm in}$  as indicated in Fig. 3. When the switch S is opened, current decreases with voltage  $(V_0 - 2V_m)$  as shown in Fig. 3. The ripple in inductor current  $i_{\rm L1}$ .

$$\Delta_{iL1} = \left(\frac{V_{in}}{L_1}\right) dT = \left(\frac{V_o - 2V_{in}}{L_1}\right) dT \tag{1}$$

$$V_{o} = \left(\frac{2-d}{1-d}\right) V_{in} \tag{2}$$

Voltage transfer gain is:

$$G = \left(\frac{V_o}{V_{in}}\right) = \left(\frac{2-d}{1-d}\right) \tag{3}$$

In steady state, the average charges across capacitor C<sub>1</sub> should not change. We have the following relations:

$$i_{i_{n-off}} = i_{1,1-off} = i_{C1-off}, i_{i_{n-on}} = i_{1,1-on} + i_{C1-on}$$

(4)

When inductance  $L_1$  is large,  $i_{L1}$  is nearly equal to average current  $i_{L1}$ . Therefore:

$$i_{\text{in-off}} = i_{\text{L1}} = i_{\text{C1-off}}, i_{\text{in-on}} = i_{\text{L1}} + \frac{1-d}{d} \frac{i_{\text{L1}}}{d}$$

(5)

$$i_{C1-on} = \frac{1-d}{d}i_{L1}$$

(6)

Average input current:

$$I_{\rm in} = di_{\rm in-on} + (1-d)i_{\rm in-off} = i_{\rm L1} + (1-d)i_{\rm L1} = (2-d)i_{\rm L1} \eqno(7)$$

Considering:

$$T = \frac{1}{f} \tag{8}$$

Fig.1: Circuit diagram of ZVS POESLLC

Fig. 2: POESLLC modes of operation

Fig. 3: Circuit diagram of POESLLC

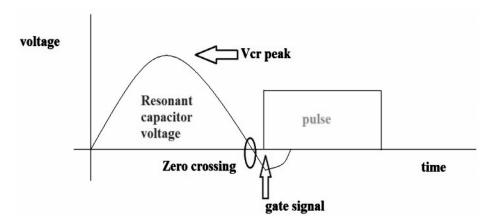

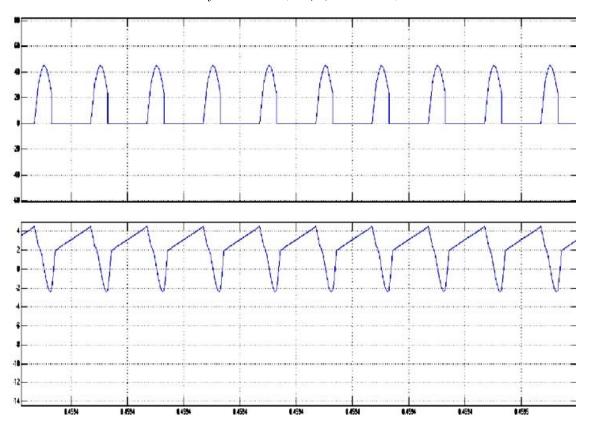

Fig. 4: Theoretical waveform showing ZVS operation

$$\frac{V_{in}}{I_{in}} = \left(\frac{(1-d)}{(2-d)}\right)^{2} \frac{V_{o}}{I_{o}} = \left(\frac{(1-d)}{(2-d)}\right)^{2} R \tag{9}$$

The variation ratio of inductor current  $i_{Li}$  is:

$$\xi = \frac{\Delta_{iL1/2}}{i_{L1}} = \frac{d(2-d)TV_{in}}{2L_{1}I_{in}} = \frac{d(1-d)^{2}}{2(2-d)}\frac{R}{fL_{1}}$$

(10)

The ripple voltage of output voltage Vo is:

$$\Delta_{V_0} = \frac{\Delta Q}{C_2} = \frac{I_o (1 - d)T}{C_2} = \frac{(1 - d)}{fC_2} \frac{V_o}{R}$$

(11)

Therefore, the variation ratio of output voltage V<sub>0</sub> is:

$$\xi = \frac{\Delta_{\text{VO}} / 2}{V_0} = \frac{(1 - d)}{2RfC_2}$$

(12)

POESLLC Under ZVS switching: The Zero Voltage Switching (ZVS) is one of the soft switching methods implemented to improve the switching efficiency. The converter can be operated at a high switching frequency using ZVS. In ZVS the voltage across the switch is shaped and it is operated to near zero voltage to minimize the losses (Jayashree and Uma, 2011abc). The voltage across switch is shaped as shown in the Fig. 4. The successful operation of ZVS in Luo and Ultra Lift Luo converters is given in study (Jayashree and Uma, 2011abc).

The closed loop operation of dc-dc converter with a VCO is shown in Fig. 5 for ZVS operation. The PI-ZVS POESLLC circuit is shown in Fig. 1 and four basic modes of operation with appropriate current direction is shown in Fig. 6.

In ZVS quasi resonant converters, the transistor peak current is identical to that of PWM converters. However, the transistor peak voltage is much higher than that of PWM converters which requires a MOSFET with a higher breakdown voltage. Such MOSFETs have a higher onresistance, causing a higher conduction loss (Kazimierczuk, 2008).

$$P_{rDS} = r_{DS} I_{Sms} \tag{13}$$

#### Design of proposed converter

**Design:** Commercial controllers can operate each phase at a switching frequency in the MHz range, resulting in effective size reduction. The Luo converter is designed for 12 V input voltage, 100 KHz. For 50% duty cycle the output voltage of the POSLLC is shown in Fig. 7-9

$$V_o = \left(\frac{2-d}{1-d}\right) V_{in}$$

$d = 0.5$  (14)

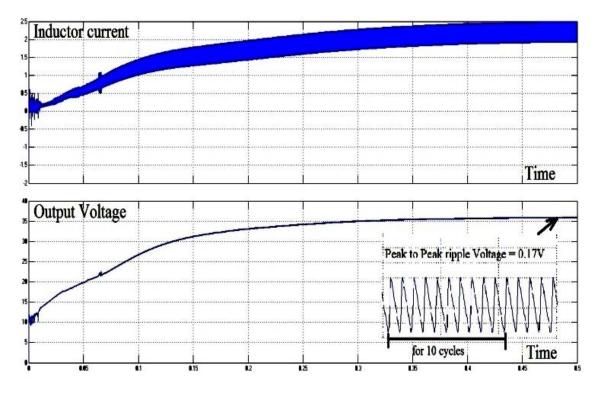

The  $V_o$ = 36 V, Let Load resistance,  $R = 50 \Omega$ , Output Current,  $I_o$ = 0.720 A, Output Power,  $P_o$ =  $V_oI_o$ = 25.920 W, Let the efficiency be 91.79%. So:

Input Power

$$P_{in} = \left(\frac{P_0}{\eta}\right) 28.238W$$

(15)

Input Current,  $I_{in}$ = 2.353A, Inductor ripple current is 25% of input current, so  $\Delta I_{Li}$ =0.6A

$$L_{1} = \left(\frac{V_{in}}{f\Delta i_{L1}}\right) d = 100 uH$$

(16)

Capacitor ripple voltage is  $\Delta v_0 = 0.16 \text{ V}$

Asian J. Inform. Technol., 15 (18): 3577-3586, 2016

Fig. 5: Block diagram for closed loop operation of ZVS-POESLLC

$$C_{o} = \left(\frac{1-d}{f\Delta V_{o}R}\right) V_{o} = 22.5 uF \tag{17}$$

Co= C1 = 22.5 uF. ence the design parameters are tabulated (Table 1).

PI control: The design and analysis of a PI control for POESLLC is given. PI controller is modeled using operational amplifier. The values of proportional gain, Kp and integral time, T<sub>I</sub> of the controller are determined using Ziegler-Nichol's tuning method. For triggering the converter, variable pulse generator is used:

Resonant frequency=

$$f_o = \frac{1}{2\pi\sqrt{L_rC_r}}$$

(18)

| Table 1: Design parameters for PO | ESLLC                     |         |

|-----------------------------------|---------------------------|---------|

| Parameter name                    | Symbol                    | Value   |

| Input voltage                     | $ m V_{in}$               | 12 V    |

| Output voltage                    | $V_{\circ}$               | 36 V    |

| Inductor                          | $\mathbf{L}_1$            | 100 μΗ  |

| Capacitors                        | $C_1, C_2$                | 30 μF   |

| Nominal switching frequency       | $\mathbf{f}_{\mathrm{s}}$ | 100 KHz |

| Load resistance                   | R                         | 50 Ω    |

| Output power                      | $P_{\circ}$               | 25.92 W |

| Input power                       | ${ m P_{in}}$             | 28.32 W |

| Average input current             | $\mathbf{I}_{	ext{in}}$   | 2.361 A |

| Efficiency                        | η                         | 91.56%  |

| Average output current            | $I_{o}$                   | 0.72 A  |

| Duty ratio                        | d                         | 0.5     |

| Peak-to-peak inductor current     | $\Delta i_{L1}$           | 0.6 A   |

| ripple                            | $\Delta  m V_o$           | 0.16 V  |

| Peak too peak capacitor ripple    |                           |         |

Characteristic impedance

$$Z_{_{0}} = \sqrt{\frac{L_{_{r}}}{C_{_{r}}}}$$

(19)

Fig. 6: ZVS-POESLLC modes of operation

Fig. 7: Simulated resonant capacitor voltage and resonant inductor current of ZVS-POESLLC

Fig. 8: Output voltage and inductor current for start-up transient of ZVS-POESLLC

Fig. 9: Output voltage and inductor current in steady state region of ZVS-POESLLC

Condition for ZVS is:

Peak switch current, ISM = MVDCIO = 2.16A (25)

$$I_{M} Z_{o} \ge V_{in} \tag{20}$$

## RESULTS AND DISCUSSION

DC voltage transfer function is:

$$M_{\text{VDC}} = \frac{V_{\text{O}}}{V_{\text{in}}} = 3 \tag{21}$$

Let  $Q = M_{VDC} = 3$

$$M_{\text{VDC}} = \frac{1.1}{f_{\text{s}}/f_{\text{o}}}$$

(22)

$f_0$  = 272.727 Khz Characteristic impedance,  $Z_0$  =  $R_L/Q$  = 16.666:

$$L_{r} = \frac{R_{L}}{\omega_{o}Q} = 9.726 \text{uH}$$

(23)

$$C_r = \frac{Q}{\omega_0 R_L} = 35.014 nF$$

(24)

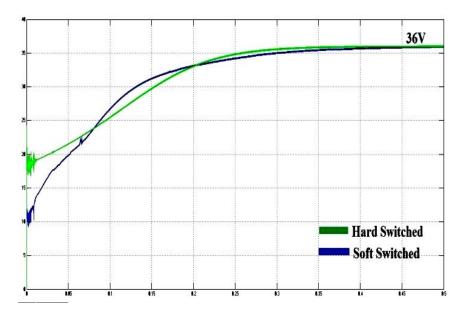

The designed converter is simulated in MATLAB-simulink platform. Simulink is graphical multi-domain simulation and Model-Based Design for dynamic and embedded systems shown in Table 2. The output voltage for PI-ZVS POESLLC is shown in Fig.10. For an input voltage of 10 V the PI controller regulates the output voltage to reference voltage of 36 V. This is achieved under zero voltage soft switching condition.

Table 2: Ripple voltage for a range of load variation

| Load current, i <sub>l</sub> | Theoretical<br>ripple<br>voltage | Simulated ripple<br>voltage for<br>hard switching | Simulated ripple<br>voltage for soft<br>switching |

|------------------------------|----------------------------------|---------------------------------------------------|---------------------------------------------------|

|                              |                                  |                                                   |                                                   |

| 0.80                         | 0.13                             | 0.18                                              | 0.20                                              |

| 0.72                         | 0.12                             | 0.15                                              | 0.18                                              |

| 0.65                         | 0.11                             | 0.14                                              | 0.17                                              |

| 0.60                         | 0.10                             | 0.12                                              | 0.15                                              |

Fig. 10: Output voltage comparison of hard and soft switched POESLLC

### CONCLUSION

In this study, the ZVS-POESLLC is compared with POESLLC analyzed and designed. The proposed topology and control technique may be used in industrial applications requiring regulated output voltage. The Positive Output Elementary Super Lift Luo Converter (POESLLC) performs the voltage conversion from positive source voltage to positive load voltage. Due to the time variations and switching nature of the power converters, their dynamic behavior becomes highly non-linear. This studyr has successfully demonstrated the design, analysis and suitability of PI-ZVS controlled positive output elementary super lift Luo converter for much efficient operation and high frequency. The positive output elementary super lift Luo converter with PI-ZVS control thus claims its use in applications such as computer peripheral equipment, switch mode power supply, medical equipments and industrial applications, especially for high voltage application etc.

## REFERENCES

Burkhart, J.M., R. Korsunsky and D.J. Perreault, 2013. Design methodology for a very high frequency resonant boost converter. IEEE. Transac. Power Electron., 28: 1929-1937.

Jayashree, E. and G. Uma, 2011a. Analysis, design and control of zero-voltage switching quasi-resonant -positive output super lift Luo converter. IET. Power Electron., 4: 21-28. Jayashree, E. and G. Uma, 2011b. Design and implementation of zero-voltageswitching quasi-resonant positive-output Luo converter using analog resonant controller UC3861. IET. Power Electron., 4: 81-88.

Jayashree, E. and G. Uma, 2011c. Soft-switchedcontrolled-ultra lift Luo converter. IET. Power Electron., 4: 151-158.

Kazimierczuk, M.K., 2008. Pulse-Width Modulated DC-DC Power Converters. John Wiley and Sons, New Delhi, India, ISBN: 9780470694657, Pages: 808.

Kumar, K.R. and S. Jeevananthan, 2010. PI control for positive output elementary super lift Luo converter. Int. J. Electr. Electron. Eng., 4: 440-445.

Kumar, K.R. and S. Jeevananthan, 2013. Design and implementation of reduced-order sliding mode controller plus proportional double integral controller for negative output elementary super-lift Luo-converter. IET. Power Elec., 6: 974-989.

Luo, F.L. and H. Ye, 2003b. Negative output super-lift converters. IEEE. Transac. Power Electronics, 18: 1113-1121.

Luo, F.L. and H. Ye, 2003a. Positive output super-lift converters. IEEE. Transac. Power Electron., 18: 105-113.

Luo, F.L. and H. Ye, 2007. Small signal analysis of energy factor and mathematical modeling for power dc-dc converters. IEEE. Transac. Power Electron., 22: 69-79.

Luo, F.L. and L.L. Fang, 2004. Advanced DC/DC Converters. CRC Press, New York, USA.,.

- Luo, F.L. and Y. Hong, 2006. Essential Dc-Dc Converters. Taylor and Francis Group, New York, USA., ISBN: 9780849372384, Pages: 420.

- Luo, F.L., 1999. Positive output Luo converters: Voltage lift technique. IEEE. Proc. Electr. Power Appl., 146: 415-432.

- Luo, F.L., 2008. Analysis of super-lift Luo-converters with capacitor voltage drop. Proceedings of the 2008 3rd IEEE Conference on Industrial Electronics and Applications, June 3-5, 2008, IEEE, Singapore, ISBN: 978-1-4244-1718-6, pp. 417-422.

- Marian, K.K. and D. Czarkowski, 2011. Resonant Power Converters. John Wiley and Sons, Hoboken, New Jersey, USA.,.

- Mohan, N. and U.M. Tore, W.P. Robbins, 2006. Power Electronics: Converters, Applications, and Design. John Wiley and Sons, Hoboken, New Jersey, USA.,.

- Zhu, M. and F.L. Luo, 2004. Analysis of positive output super-lift converter in discontinuous conduction mode. Proceedings of the International Conference on Power System Technology, November 21-24, 2004, IEEE, New York, USA., ISBN: 0-7803-8610-8, pp: 828-833.