ISSN: 1682-3915

© Medwell Journals, 2016

# **Hybrid Architecture for Overlapped Test Vector Compression**

<sup>1</sup>S. Rooban and <sup>2</sup>R. Manimegalai <sup>1</sup>Department of Electronics and Communication Engineering, Sri Krishna Institute of Technology, 601301 Chennai, India <sup>2</sup>Department of Computer Science and Engineering, Park College of Engineering and Technology, 641659 Coimbatore, India

**Abstract:** This study depicts novel programmable low power test data compression architecture that permits formation of entropy encoded test scan envelope with exact and adaptable design in context of achieving continuous adjustment with the overlapped test vectors. The proposed architecture proficiently consolidates test compression with logic gates where both software and hardware strategies can work synergistically to convey top-notch test vector compression. Experimental results got from the simulation of proposed architecture add attainability of the proposed scheme and are accounted for test vector compression using hybrid i.e., both hardware and software based test data compression.

**Key words:** Built-in self-test, hybrid low power compression, low power test, test data compression, scan-based test, toggling

### INTRODUCTION

Despite the fact that the essential goal of manufacturing, testing will remain basically the same to guarantee reliable and superb semiconductor items conditions and therefore test arrangements may experience a noteworthy advancement throughout the following years. The semiconductor innovation, outline qualities and the configuration procedure are among the key variables that will affect this development. With new sorts of imperfections that one will need to consider to give the sought test quality to the following innovation hubs, for example, 3D, it is suitable to offer the conversation starter of what matching Design For Testability (DFT) techniques should be conveyed.

Test compression, introduced ten years back, rapidly turned into the main stream DFT technique. In any case, it is vague whether test compression will be fit for coping with the quick rate of technological changes throughout the following decade. Interestingly, Logic Built-In Self-Test (LBIST) originally created for board, framework and in-field test is currently gaining acknowledgment for production test as it gives extremely hearty DFT and is utilized increasingly frequently with test compression. This half and half approach is by all accounts the following logical evolutionary stride in DFT. It has the potential for enhanced test quality; it might incredibly expand the capacities to keep running in

conjunction with power aware tests and it can diminish the expense of manufacturing test while preserving all LBIST and scan compression focal points.

Endeavours to defeat the bottleneck of test data transmission capacity between the tester and the chip have made the idea of combining logic BIST and test data compression exceptionally basic innovative work territory. Specifically, a few cross breed BIST plans store deterministic top-up patterns (used to identify random pattern safe issues) on the tester in a compacted form and afterward utilize the existing BIST hardware to decompress these test patterns (Das and Touba, 2000; Dorsch and Wunderlich, 2001; Ichino et al., 2001; Krishna and Touba, 2003; Wohl et al., 2003; Jas et al., 2004; Li and Chakrabarty, 2005). A few arrangements install deterministic boosts by using packed weights or by perturbing the pseudorandom vectors in different styles (Wunderlich et al., 1996; Hellebrand et al., 2001; Liang and Kiefer, 2002; Touba and McCluskey, 2001; Li and Chakrabarty, 2004; Hakmi et al., 2007). On and off chance that BIST logic is utilized to convey compacted test data, then underlying encoding plots ordinarily exploit low fill rates as originally proposed in LFSR coding which hence static advanced first into LFSR (Hellabrand et al., 1995, 2001; Krishna and Touba, 2002; Gherman et al., 2004; Wang and Chakrabarty, 2006; Wohl et al., 2005; Hakmi et al., 2009) and afterward into element LFSR reseeding (Barnhart et al., 2002;

Rajski et al., 2004). The careful studies of important test compression procedures can be found, for instance by Touba (2006) and Kapur et al. (2008). Likewise with ordinary scan-based test, half breed plans may expend more power than a circuit-under-test is appraised for. The resulting overheating or supply voltage commotion can bring about a gadget glitch, hence yield misfortune, increased chip dependability debasement, shorter item lifetime or even a lasting harm. Low power test compression plans (Rosinger et al., 2002); Lee and Touba, 2007; Wu et al., 2008; Liu and Xu, 2009) adjust again LFSR reseeding to diminish scan-in moves as the low fill rates make it conceivable to convey indistinguishable test data to scan chains for various movement cycles specifically from the decompressor, in this manner reducing the quantity of moves. Thus, low-move test pattern generators are key parts of numerous power aware BIST arrangements (Girard et al., 2001, 2010; Tehranipoor et al., 2005; Wang and Chakrabarty, 2006; Lin and Rajski 2010). Ordinarily, they utilize LFSRs to sustain scan chains through some kind of biasing logic such that the same qualities are more than once moved into scan chains for various movement cycles. Other BIST plans go for keeping the normal and crest power beneath a given limit by using gating logic to keep moves at memory components from propagating to combinational logic during scan shift (Gerstendorfer and Wunderlich, 2000; Zoellin et al., 2006). An exhaustive perspective of the low power test zone is given by Girard et al. (2001, 2010). Pseudorandom test patterns produced with desired toggling levels and enhanced fault coverage gradient compared with the best-to-date Built-In-Self-Test (BIST) based pseudorandom test pattern generators is achieved by a Low Power (LP) programmable generator described in (Filibek et al., 2015).

As of late, a Pseudorandom Test Pattern Generator (PRPG) was proposed for low power BIST applications (Solecki et al., 2012). The generator goes for reducing the switching action during scan loading. The exceptionally same generator permits completely mechanized choice of its controls so that the resultant test patterns highlight craved preselected toggling rates. In this study, we exhibit that the same generator can likewise effectively go about as a test data decompressor, along these lines allowing one to execute a crossover test approach that combines LBIST and ATPG-based implanted test compression. This is the principal low power test compression conspire that gives originators a chance to shape the power envelope in a completely unsurprising, precise and adaptable design. Additionally, both strategies can supplement each other to address, for instance, a voltage drop brought on by a high switching movement during scan testing, constraints of at-speed ATPG-delivered test patterns or new blame models. As said before, this paper introduces a completely programmable low power test compression conspire that is integrated in each route with a power aware pseudorandom test pattern generator.

### MATERIALS AND METHODS

Experimental Setup: Keeping in mind the end goal to exhibit the viability of the proposed test compression architecture, independent simulations were conducted. An automatic test generation project was first utilized for obtaining a set of test vectors giving 100% fault scope. The proposed compression architect was implemented in MATLAB programming environment on a Windows machine having Quad-center 2.5-GHz Ultra processor with 8GBs of RAM. On account of space constraints, only some partial results of the circuits are given. All the test vectors required for testing the SOC are first compacted in software mode. The packed test vectors and an efficient decompression system are then stacked into the simulation of embedded handling core of the SOC. The processor executes the decompression process and afterward applies all the uncompressed unique test vectors to every centre of SOC for generating and breaking down the output responses.

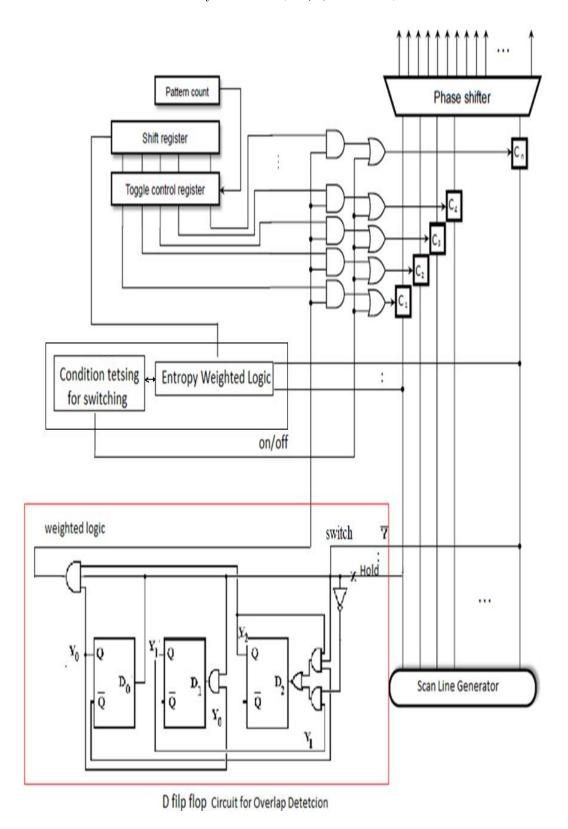

**Architecture for test data compression:** Figure 1 shows the proposed Simulink architecture for test data compression. In this compression technique all the test vectors are divided into several blocks comprising of equal size where the size of this blocks depends on the proportionality of bits in each vector. Here, the idea of compression is that primarily passed test vectors are considered as reference test vectors whereas the consequent vectors are generated from the weighted evaluation of the referenced one by storing those blocks/bits that exhibits difference with it. This will allow us to compress and recover the whole set of test vectors during the decompression process. The entropy of the test data is compressed using the estimated weighted factors deduced from the presented algorithm. It is applied for compression on test data set as a matrix of size m x n. Here, scan line generator block is used to generate several scan lines based on the following logic. Each of the rows belonging to C scan lines are divided into blocks of equal size. Owing to the structural relationships among the faults there tends to be many similarities between test vectors. Hence, this test vectors can be ordered optimally such that the successive test vectors experience difference by just a fewer number of blocks. Thereby, reducing the amount of information is requisite for storing these differences will comparatively fall beyond the size required for storing the entire test vectors.

Fig. 1: Simulink block diagram of test vector compression

Fig. 2: Mechanism of overlapping bit compression using d flip flop based circuitry

Let  $C_k$ , be the test vectors where k = 1,2,3,...n of size  $m \times n$  and N is the block size of data. Thus, the entropy of this test vector can be represented in Eq 1:

$$E(C_{K}) = \sum_{i=1}^{n} P_{i} * log_{2} P_{i}$$

(1)

Where:

$C_K = \{C_1, C_2, ... C_n\}$

$P_i$  = The index of bits

$b_K$  = The weighted indices distances corresponding between the adjacent blocks of the test vectors

Since, the distribution changes with time, therefore it is necessary to use an encoding scheme with respect to the changing time. Thus, the distance frequency for the distribution of indexes needs optimum parameters for each  $C_K$  and  $C_K$  respectively. This correspond to the hard problem because of the increase in size relegates the necessity of general solution. Thus, for a given k distance of good vectors, the problem is in the fact that how we will encode each section of the scan vectors and what is the best parameter for reducing the size of encoded data is derived from EHMCA (Entropic Hidden Markov Chain Algorithm); where the data needs to be pre-processed or divided into scan lines of test vectors using Eq. 2:

$$C_{K} = -\sum_{i=1}^{m} C_{0}(K_{i}) + \sum_{i=1}^{K_{i}} C_{0}(b_{i}) + \dots + \sum_{i=K_{m-1}+1}^{K} C_{m}(b_{i})$$

(2)

Where:

C<sub>i</sub>(.) = The required size to encode the indices value at each section

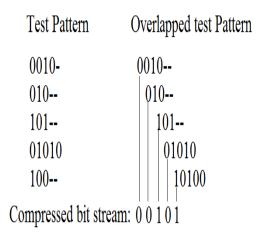

Having instantiated the generated scan lines the data is dispatched to the D flip flop based overlap detection circuitry. The mechanism of bit overlapping is illustrated in the Fig. 2. This architecture by and large tries to discover bordering and continuous test bit patterns having the most maximum overlap. Deterministic test examples are created by an ATPG and compacted. Pattern in the scan chain are checked whether they coordinate with one or more test examples which were not utilized in the sequence yet. The comparing rundown of transitions is utilized to touch base with the underlying span of the switching, hold and weighted equalizer logic as the yield. These qualities are picked conservatively such that the proportion switching/hold is insignificant and there are no transitions inside a solitary hold period. The previous condition guarantees that the given template can at present oblige some of recently delivered test solid shapes. The last condition can be reworded as takes after: for every move either its range is more noteworthy than hold period or possibly one of its flanking bits exists in a switching period.

Followed by the process of compressing overlapped bits separately, the weight indices of the derivative bits are checked under module named condition testing for switching; where the optimum weighted parameter is determined using the following EHMCA algorithm. The algorithm is explained as follows. We assume the  $P(C_K | C_{K-1})$  is independent of K which leads to the definition of the stochastic transition matrix  $K = \{K_{ij}\} = P(C = j | C_{K-1} = i)$ . The initial state distribution of the primary test vector (i.e. when K = 1) is given in Eq. 3:

$$t_i = P(C_1 = i) \tag{3}$$

The observation variables  $0_K$  can take one of K possible values. The probability of a certain observation at K index for state j is obtained by Eq. 4:

$$b_{i}(0_{k}) = P(0_{k} = 0, |C_{k} = j)$$

(4)

Taking into account all the possible values of  $0_K$  and  $C_K$  we obtain the weighted  $b_K$  i.e., indices distances corresponding between the adjacent blocks by N matrix An observation sequence is given by. Thus, we can describe a hidden Markov chain by initializing the computing with  $\theta = (C, 0, \tau)$  iteratively updating for local weighted maximum for. Algorithm: Entropic Hidden Markov Chain Algorithm (EHMCA) for test data:

Input: entropy based divided test vectors

**Output:** compressed test vectors and is the expected weighted indices distance corresponding between the adjacent blocks of the test vectors.

**Step 1:** Set  $\theta = (C, 0, \tau)$  with random initial conditions by using prior information of primary test vector.

**Step 2:** Recursively determine the probability for the continued manifestation of bits. Let  $\alpha_i(K) = P(0_1, 0_2 = 0_2,..., 0_T = 0_T, C_K = I | \theta)$ , the probability of appearing  $0_1, 0_2,..., 0_K$  the and being in state i at time K and j at time K+1 is represented in Eq 5 and 6:

$$a_{i}(1) = t_{i}b_{i}(0_{1})$$

(5)

$$a_i(K+1) = b_i(0_{t+1}) \sum_{i=1}^{N} a_i(K) a_{ij}$$

(6)

**Step 3:** Calculate the temporary variables from the test vectors, by evaluating the transition probability of bit being in state i at time K given the spotted sequence O and the parameters  $\theta$  (using the Bayes' theorem) is given in Eq. 7:

$$T_i(K) = P(C_k = i | 0,?)$$

(7)

**Step 4:** Calculate the probability of being in state i and j at times K and K+1 respectively given the observed sequence O and parameters  $\theta$  by the Eq 8:

$$f_{ii}(K) = P(C_K = i, C_{K+1} = j | 0,?)$$

(8)

**Step 5:** Update  $\theta$  in order to resolve the expected number of transitions from state i to state j in comparison to the expected total number of shifts away from state i using Eq 9:  $t_i^* = T_i(1)$  Expected frequency spent in state i at time 1:

$$t_{ij}^* = \frac{\sum_{K=1}^{K-1} f_{ij}(t)}{\sum_{K=1}^{K-1} T_i(t)}$$

(9)

**Step 6:** Compress the bits by replacing 1 or 0 with r and simultaneously determining the final weighted vectors for the number of shifts away from state i that do not mean transitions to a different state j but but to any state including it self using Eq. 10. This is corresponding to the no of times state i is detected in the sequence from K = 1 to K-1:

$$b_{K}^{*}(r) = \frac{\sum_{k=1}^{K} 1_{0K=r} T_{i}(k)}{\sum_{i=1}^{T-1} T_{i}(K)}$$

(10)

where,  $b_{\kappa}^*$  is the expected weighted indices distance corresponding between the adjacent blocks of the test

vectors such that the number of times the output observations have been equal to while in state i over the expected total number of times in state i by Eq 11:

$$1_{0K=r} = \begin{cases} 1, & \text{if } 0_{K} = r \\ 0 & \text{otherwise} \end{cases}$$

(11)

**Step 7:** Repeat Steps 4-6 iteratively until  $P(0|\theta_{\text{final}}) > P(0|\theta)$  is reached.

**Step 8:** Recalculate the entropy of the compressed test vector using Eq 12.

$$E(o_{K}) = -\sum_{i=1}^{n} P_{i} * log_{2} P_{i} / / for 0_{K} = \{0_{1}, 0_{2}, ... 0_{n}\}$$

(12)

where,  $p_i = p_{i-1} + b_k^*$ .

Step 9: Stop Having set all up important conditions, one can continue with the test specified bit encoding through the mix of shifting and counting the pattern of bits through the shift register, pattern count module over toggling of register control. This achieved in a way like that of the ordinary EDT stream. It is significant, notwithstanding, that interest of a given test bit pattern in a template does not ensure its real combining and pressure in view of either bit clashes on certain predetermined bits with other test blocks or constrained encoding abilities. Another prominent distinction between the displayed approach and a conventional EDT plan is the way compression process is aborted. Here, the test bit pattern is encoded with different weighted indices, to frame a template, which thusly alters conditions. Consequently, all the processed bit is accounted for low power consuming template and is then picked as the main part of a test vector. All compacted test scan lines are expelled from the entropy encoded bit pool, through the phase shifter module otherwise the computation proceeds by making another arrangement of templates until the length of the pool is not vacant. Once the above technique finishes, one need to ensure that all scan chains facilitating transitions are enabled. This can be accomplished for the length of time until there is no less than one switch enable phase shifter switching input that nourishes a given scan through a XOR logic gateway inside the phase shifter. Finding the insignificant subset of the switch control register stages expected to enact the required scan chains is equal to taking care of the minimum hitting set problem. In this study, we used the greedy approach to come up with the optimized solution of the problem.

In comparison with the desired switching ratio on/off chance that the resultant switching is underneath the ratio, then the weighted test template pattern for compression encoding can be at last acknowledged as a part of the template. Or else, the weighted test pattern is not compressible given the encoding constraints and must be disposed of. The weighted template comes back to its underlying status. When the total sum of templates has been initialised, the circuitry endeavours to connect the encoded bit with the rest of test bits. On the off a chance that template cannot oblige certain transitions included by a recently picked test vector, then the spans of switch, hold, and counterbalance periods can be further balanced. On the off chance that the test bits fits to the template and new dynamic scan chains are known, then we recalculate both the substance of the flip control register and the switching rate. Once more, if the switching is above, then the template comes back to its past structure, while the test bit scan line is gone to the following template. Besides, if none of the current templates can oblige the block, it stays in the pool until another arrangement of templates is produced such that this specific scan line can be in the long run allotted to its assigned LPT.

## RESULTS AND DISCUSSION

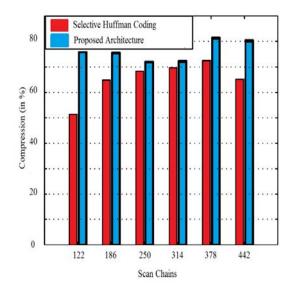

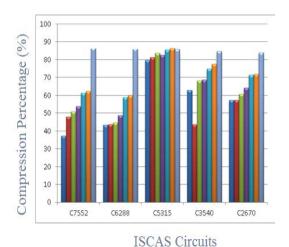

The investigation results reported here evaluates execution of the new compression architecture. Trials are made on a few industrial circuitries whose qualities, including scan architecture. Figure 3 and 4 are given in Table 1. Simulation results obtained from simulink simulator presents after effects of investigations led with 64-bit compressor and the fancied scan shift-in switching level set to 15, 20 and 25%. For scan shift operations, the normal Weighted Transition Metric (WTM) gauges the resultant switching action by checking the quantity of conjured transitions in scan cells and considering their relative positions. To quantify flipping in the catch mode, the switching action at every door in the circuit is recorded by method for the normal Weighted Switching Activity (WSA). All investigations are directed in a manner that the first EDT-based test scope is constantly protected. We have additionally watched a comparable pattern for other switching rates in each test situation. It is important that diminishing the heap switching positively affect switching action amid catch and emptying of scan chains. This is additionally worth watching that the proposed arrangement is the principal low power pressure plot that offers an instrument to shape the force envelope in such an adaptable and precise style.

Table 1: Compression and Power Reduction Percentage of Experimented ISCAS'89 Benchmark

| Test Si. | Total original | Output compressed | Comp ression | Power reduction |

|----------|----------------|-------------------|--------------|-----------------|

| No       | bits           | bits              | (%)          | (%)             |

| C7552    | 2934           | 427               | 85.43        | 73.05           |

| C6288    | 3342           | 516               | 84.54        | 77.03           |

| C5315    | 3832           | 562               | 85.32        | 79.04           |

| C3540    | 4786           | 754               | 84.23        | 78.06           |

| C2670    | 5679           | 1002              | 82.34        | 78.07           |

Fig. 3: Compression performance plot of the proposed architecture for different sizes of scan chains

Fig. 4: Compression of performance with proposed method and that of past method in the literature

### CONCLUSION

As presented in the study, the recently discussed low power architecture is equipped for as a completely

practical test data compressor with capacity to decisively control scan shift-in switching action through the procedure of encoding, its low power test logic requires impressively littler measure of silicon land than that of the current low power compression plans. The proposed arrangement allows one to effectively consolidate test compression with programming based compression logic where both strategies can work synergistically to convey excellent test. It is along these lines an extremely appealing low power test plot that allows for exchanging off test scope, sum of patterns and flipping rates.

### REFERENCES

- Barnhart, C., V. Brunkhorst, F. Distler, O. Farnsworth and A. Ferko et al., 2002. Extending OPMISR beyond 10x scan test efficiency. IEEE. Des. Test, 19: 65-72.

- Das, D. and N.A. Touba, 2000. Reducing test data volume using external/LBIST hybrid test patterns. Proceedings of the International Conference on Test, October 5-5, 2000, IEEE, Austin, Texas, USA, ISBN:0-7803-6546-1, pp: 115-122.

- Dorsch, R. and H.J. Wunderlich, 2001. Tailoring ATPG for embedded testing. Proceedings of the International Conference on Test, November 1-1, 2001, IEEE, Germany, ISBN:0-7803-7169-0, pp. 530-537.

- Filipek, M., G. Mrugalski, N. Mukherjee, D.B. Nadeau and J. Rajski et al., 2015. Low-power programmable PRPG with test compression capabilities. IEEE. Trans. Very Large Scale Integr. Syst., 23: 1063-1076.

- Gerstendorfer, S. and H.J. Wunderlich, 2000. Minimized power consumption for scan-based BIST. J. Electron. Test., 16: 203-212.

- Gherman, V., H.J. Wunderlich, H. Vranken, F. Hapke and M. Wittke et al., 2004. Efficient pattern mapping for deterministic logic BIST. Proceedings of the International Conference on Test ITC-2004, October 26-28, 2004, IEEE, Germany, ISBN:0-7803-8580-2, pp: 48-56.

- Girard, P., L. Guiller, C. Landrault, S. Pravossoudovitch and H.J. Wunderlich, 2001. A modified clock scheme for a low power BIST test pattern generator. Proceedings of the 19th VLSI Test Symposium, April 29-May-3, 2001, Marina Del Rey, CA., pp. 306-311.

- Girard, P., N. Nicolici and X. Wen, 2010. Power-Aware Testing and Test Strategies for Low Power Devices. Springer Berlin, Germany, ISBN:978-1-4419-0927-5, Pages: 357.

- Hakmi, A.W., H.J. Wunderlich, C.G. Zoellin, A. Glowatz and F. Hapke, 2007. Programmable deterministic built-in self-test. Proceedings of the 2007 IEEE International Conference on Test, October 21-26, 2007, IEEE, Hamburg, Germany, ISBN: 978-1-4244-1127-6, pp: 1-9.

- Hakmi, A.W., S. Holst, J. Schloffel, F. Hapke and H.J. Wunderlich et al., 2009. Restrict encoding for mixed-mode bist. Proceedings of the 27th IEEE Symposium on VLSI Test, May 3-7, 2009, IEEE, Hamburg, Germany, pp. 179-184.

- Hellebrand, S., H.G. Liang and H.J. Wunderlich, 2001. A mixed mode BIST scheme based on reseeding of folding counters. J. Electron. Test., 17: 341-349.

- Hellebrand, S., J. Rajski, S. Tarnick, S. Venkataraman and B. Courtois, 1995. Built-in test for circuits with scan based on reseeding of multiple-polynomial linear feedback shift registers. IEEE. Trans. Comput., 44: 223-233.

- Ichino, K., T. Asakawa, S. Fukumoto, K. Iwasaki and S. Kajihara, 2001. Hybrid BIST using partially rotational scan. Proceedings of the 2001 10th Asian Symposium on Test, November 19-21, 2001, IEEE, Japan, ISBN:0-7695-1378-6, pp: 379-384.

- Jas, A., C.V. Krishna and N.A. Touba, 2004. Weighted pseudorandom hybrid BIST. IEEE. Trans. Very Large Scale Integr. Syst., 12: 1277-1283.

- Kapur, R., S. Mitra and T.W. Williams, 2008. Historical perspective on scan compression. IEEE Design Test Comput., 25: 114-120.

- Krishna, C.V. and N.A. Touba, 2002. Reducing test data volume using LFSR reseeding with seed compression. Proceedings of the International Conference on Test, October 10-10, 2001, IEEE, Austin, Texas, USA, ISBN:0-7803-7542-4, pp. 321-330.

- Krishna, C.V. and N.A. Touba, 2003. Hybrid BIST using an incrementally guided LFSR. Proceedings of the 18th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, November 5-5, 2003, IEEE, Austin, Texas, USA, ISBN:0-7695-2042-1, pp: 217-224.

- Lee, J. and N.A. Touba, 2007. LFSR-reseeding scheme achieving low-power dissipation during test. IEEE. Trans. Comput. Aided Des. Integr. Circ. Syst., 26: 396-401.

- Li, L. and K. Chakrabarty, 2004. Test set embedding for deterministic BIST using a reconfigurable interconnection network. IEEE. Trans. Comput. Aided Des. Integr. Circ. Syst., 23: 1289-1305.

- Li, L. and K. Chakrabarty, 2005. Hybrid BIST based on repeating sequences and cluster analysis. Proceedings of the Conference on Design, Automation and Test in Europe, March 7-11, 2005, IEEE, Austin, Texas, ISBN: 0-7695-2288-2, pp: 1142-1147.

- Liang, H.G., S. Hellebrand and H.J. Wunderlich, 2002. Two-dimensional test data compression for scan-based deterministic BIST. J. Electron. Test., 18: 159-170.

- Lin, X. and J. Rajski, 2010. Adaptive low shift power test pattern generator for logic BIST. Proceedings of the 2010 19th IEEE Symposium on Asian Test, December 1-4, 2010, IEEE, Wilsonvill, Oregon, USA, ISBN:978-1-4244-8841-4, pp. 355-360.

- Liu, X. and Q. Xu, 2009. On simultaneous shift-and capture-power reduction in linear decompressor-based test compression environment. Proceedings of the 2009 International Conference on Test, November 1-6, 2009, IEEE, China, ISBN:978-1-4244-4868-5, pp. 1-10.

- Rajski, J., J. Tyszer, M. Kassab and N. Mukherjee, 2004. Embedded deterministic test. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst., 23: 776-792.

- Rosinger, P.M., A.B.M. Hashimi and N. Nicolici, 2002. Low power mixed-mode BIST based on mask pattern generation using dual LFSR re-seeding. Proceedings of the 2002 IEEE International Conference on Computer Design: VLSI in Computers and Processors, September 18-18, 2002, September 18-18, 2002, pp: 474-479.

- Solecki, J., J. Tyszer, G. Mrugalski, N. Mukherjee and J. Rajski, 2012. Low power programmable PRPG with enhanced fault coverage gradient. Proceedings of the 2012 IEEE International Conference on Test, November 5-8, 2012, IEEE, Wilsonville, Oregon, USA, ISBN:978-1-4673-1594-4, pp. 1-9.

- Tehranipoor, M., M. Nourani and N. Ahmed, 2005. Low transition LFSR for BIST-based applications. Proceedings of the 14th Asian Symposium on Test (ATS'05), December 18-21, 2005, IEEE, Maryland, ISBN: 0-7695-2481-8, pp: 138-143.

- Touba, N.A. and E.J. McCluskey, 2001. Bit-fixing in pseudorandom sequences for scan BIST. IEEE. Trans. Comput. Aided Des. Integr. Circ. Syst., 20: 545-555.

- Touba, N.A., 2006. Survey of test vector compression techniques. IEEE Des. Test Comput., 23: 294-303.

- Wang, S. and S.K. Gupta, 1999. LT-RTPG: A new test-per-scan BIST TPG for low heat dissipation. Proceedings of the International Test Conference, September 28-30, 1999, Atlantic City, NJ., pp. 85-94.

- Wang, Z. and K. Chakrabarty, 2006. Test data compression for IP embedded cores using selective encoding of scan slices. Proceedings of the IEEE International Conference on Test, November 8-8, 2005, IEEE, Austin, Texas, ISBN: 0-7803-9038-5, pp: 10-590.

- Wohl, P., J.A. Waicukauski, S. Patel and M.B. Amin, 2003.

X-tolerant compression and application of scan-ATPG patterns in a BIST architecture.

Proceedings of the International Conference on Test, October 6-10, 2003, IEEE, california, USA., pp: 727-736.

- Wohl, P., J.A. Waicukauski, S. Patel, F. DaSilva and T.W. Williams et al., 2005. Efficient compression of deterministic patterns into multiple PRPG seeds. Proceedings of the IEEE International Conference on Test, November 8-8, 2005, IEEE, California, USA, ISBN: 0-7803-9038-5, pp: 10-10.

- Wu, M.F., J.L. Huang, X. Wen and K. Miyase, 2008. Reducing power supply noise in linear-decompressor-based test data compression environment for at-speed scan testing. Proceedings of the 2008 IEEE International Conference Test, October 28-30, 2008, IEEE, Taiwan, ISBN: 978-1-4244-2402-3, pp: 1-10.

- Wunderlich, H.J. and G. Kiefer, 1996. Bit-flipping BIST. Proceedings of the 1996 IEEE/ACM International Conference on Computer-Aided Design, November 10-14, 1996, IEEE, San Jose, California, USA, ISBN:0-8186-7597-7, pp: 337-343.

- Zoellin, C., H.J. Wunderlich, N. Maeding and J. Leenstra, 2006. BIST power reduction using scan-chain disable in the cell processor. Proceedigs of the 2006 IEEE International Conference on Test, October 22-27, 2006, IEEE, Germany, ISBN: 1-4244-0291-3, pp: 1-8.