# Study of Waveform Sampling Front-End ASIC Development for GSO/APD with DOI Information

M.N. Islam, M.S. Alam and M.A.S. Haque Institute of Electronics, Atomic Energy Research Establishment, Bangladesh Atomic Energy Commission, P.O. Box No. 3787, Dhaka, Bangladesh

**Key words:** PET, APD, DOI, WSFE, Application Specific Integrated Circuit (ASIC)

## **Corresponding Author:**

M.N. Islam Institute of Electronics, Atomic Energy Research Establishment, Bangladesh Atomic Energy Commission, P.O. Box No. 3787, Dhaka, Bangladesh

Page No: 1-3 Volume: 15, Issue 1, 2022 ISSN: 1997-5422 International Journal of Systems Signal Control and Engineering Application Copy Right: Medwell Publications

#### INTRODUCTION

An Application-Specific Integrated Circuit (ASIC) is an Integrated Circuit (IC) chip customized for a particular use, rather than intended for general-purpose one. ASIC chips are typically fabricated using Metal-oxide-Semiconductor (MOS) technology as MOS integrated circuit chips. The maximum complexity (and hence functionality) possible in an ASIC has grown from 5,000 logic gates to over 100 million. Modern ASICs often include entire microprocessors, memory blocks including ROM, RAM, EEPROM, flash memory and other large building blocks. The detector module for animal PET based on APDs has been described followed by the Abstract: Study of Waveform Sampling Front-End (WSFE) Application Specific Integrated Circuit (ASIC) development for GSO/APD with DOI Information has been presented in this research. This study confined to a detector module multi-array avalanche photodiodes (APD) with GSO crystal for high resolution animal PET, Depth-of-Interaction (DOI) information by pulse shape discrimination and multi-channel waveform sampling front-end ASIC. Study reveals that APD has shown better performance compared with PMTs for a given geometry and radiopharmaceuticals while individual readout of detector have better resolution and counting rate over light sharing or charge division schemes. Each channel of the WSFE ASIC which has been fabricated on a 4.9×4.9 mm wafer using Rohm 0.35 µ CMOS ASIC development technology comprises of a preamplifier, a Variable Gain Amplifier (VGA) and a fast Analog to Digital Converter (ADC) to digitize signals from the APD. Micrograph, design specifications, performance and test results of the WSFE chip for individual components have been presented as well.

designs and test results of a prototype and an improved front-end ASIC. Finally, the test results from several preamplifiers fabricated in a separate chip are reported<sup>[1]</sup>.

By Yeom *et al.*<sup>[2]</sup>, the test results of a new 9-channel Waveform Sampling Front-End (WSFE) ASIC and experiments performed with this chip for readout of GSO scintillating crystal coupled to an avalanche photo-diode (APD). Study of micrograph, design specifications, performance and results of the waveform sampling frontend (WSFE) application specific integrated circuit (ASIC) development with GSO/APD as well as DOI Information for individual components have been presented in the current research.

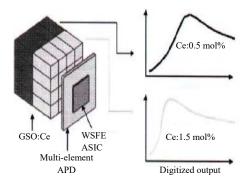

Fig. 1: The proposed detector module for DOI information. A third layer of GSO with Ce doping of 1.0 mol% can be added if pulse shape discrimination is possible

# METHODOLOGY

Study of Waveform Sampling Front-End (WSFE) Application Specific Integrated Circuit (ASIC) development for GSO/APD with DOI Information has been presented in this research. As the choice of scintillators for the detector, GSO:Ce is a promising choice because the concentration of Ce dopant determines its decay time<sup>[3]</sup>. GSO with Ce-dopant concentrations of 0.5 and 1.5 mol.% has decay time constants of 60 and 35 nsec, respectively. The proposed detector module is shown in Fig. 1. Each detector module consists of two or more crystal types with different decay times that are stacked as in a phoswich detector where each crystal of the bottom layer is coupled to a pixel of a multi-element APD for individual readout<sup>[4]</sup>.

# DESIGN SPECIFICATIONS OFTHE WSFE CHIP

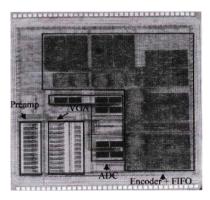

The 10-channel WSFE ASIC has been fabricated on a 4.9×4.9 mm die using Rohm 0. 35  $\mu$  CMOS ASIC technology through VLSI Education and Development Center of the University of Tokyo. The micrograph of the WSFE ASIC has been shown in Fig. 2.

**Preamplifier:** The preamplifier is based on the telescopic cascade topology<sup>[5]</sup>. The performance of the preamplifier is summarized in Table 1.

**VGA:** The input stage of the VGA is the same as that of the preamplifier to eliminate offset errors. The gain can be varied through two external pins and the results are shown in Table 2. The 10-90% rise time is 20 nsec.

**ADC:** Since, the ADC consumes the most power in the WSFE chip, a 6-bit folding ADC which greatly reduces the number of comparators (7) needed compared to a flash ADC (63) has been implemented<sup>[6]</sup>. The folding ADC

Fig. 2: Micrograph of the 10-ch WSFE ASIC

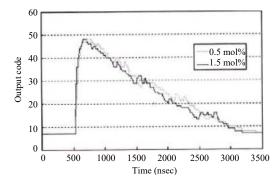

Fig. 3: Typical digitized output of GSO crystals with 0. 5 and 1. 5 mol% Ce doping seen in a logic analyzer

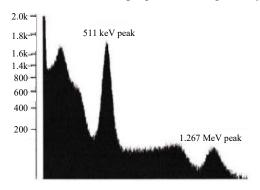

Fig. 4: Energy Spectrum of Na-22 source obtained at 360 V

Table 1: Summary of preamplifier parameters

| parameters                                                    |

|---------------------------------------------------------------|

| Specification                                                 |

| 1.2/pF                                                        |

| $20 \operatorname{nsec} (\operatorname{Cin} = 0 \mathrm{pF})$ |

| <0.5% (-0.6 to 1.5 pC)                                        |

| 1130 e <sup>+</sup> 35e <sup>-</sup> /pF FWHM                 |

|                                                               |

was tested to be working up to 60 M samples/s. However, all experiments in this report were performed with a 50 MHz clock. The differential nonlinearity (DNL) and integral nonlinearity (INL) are 1.1 and 1.4 LSB, respectively (Fig. 3-5).

Fig. 5: The 40-ch WSFE board made with prototype WSFE ASICs. The board consists of four bare chips, a FPGA (Altera Flex) and USB controller, etc.

| Table 2: First stage of the VGA |      |

|---------------------------------|------|

| VGA gain control input          | Gain |

| 00                              | 3.6  |

| 01                              | 6.9  |

| 10                              | 10.0 |

| <u>11</u>                       | 12.7 |

# CONCLUSION

The article Yeom *et al.*<sup>[1]</sup> reported that each component of the prototype WSFE chip was working with the insufficient performance for their system. After careful considerations of the layouts and testability of the chip, a significantly improved second chip was fabricated, although, further modifications seem inevitable. Yeom *et al.*<sup>[2]</sup> described that multi-channel WSFE ASIC chip has been successfully developed to readout and digitized signals from individual pixel of a multi-array APD. The rising edge of signals from 0.5 and 1.5 mol% Ce-doped GSO crystals could be distinguished for DOI information. A board has been developed with prototype WSFE chips for this purpose.

## REFERENCES

- Yeom, J.Y., H. Takahashi, T. Ishitsu, M. Nakazawa and H. Murayama, 2004. Development of a multi-channel waveform sampling ASIC for animal PET with DOI information. Nucl. Instrum. Methods Phys. Res., Sect. A., 525: 221-224.

- 02. Yeom, J.Y., K. Shimazoe, H. Takahashi and H. Murayama, 2007. A waveform sampling front-end ASIC for readout of GSO/APD with DOI information. Nucl. Instrum. Methods Phys. Res., Sect. A 571: 381-384.

- 03. Ishibashi, H., K. Shimizu, K. Susa and S. Kubota, 1989. Cerium doped GSO scintillators and its application to position sensitive detectors. IEEE Trans. Nucl. Sci., 36: 170-172.

- Inadama, N., H. Murayama, T. Omura, T. Yamashita, S. Yamamoto *et al.*, 2002. A depth of interaction detector for PET with GSO crystals doped with different amounts of Ce. IEEE Trans. Nucl. Sci., 49: 629-633.

- Gray, P.R., P.J. Hurst, S.H. Lewisa and R.G. Meyer, 2001. Analysis and Design of Analog Integrated Circuits. 4th Edn., Wiley, New York, USA., Pages: 896.

- 06. Flynn, M.P. and B. Sheahan, 1998. A 400-M sample/s, 6-b CMOS folding and interpolating ADC. IEEE J. Solid-State Circuits, 33: 1932-1938.