# Asian Journal of Scientific Research

ISSN 1992-1454

Asian Journal of Scientific Research 7 (1): 118-124, 2014 ISSN 1992-1454 / DOI: 10.3923/ajsr.2014.118.124 © 2014 Asian Network for Scientific Information

# Implementation of a 32-bit High Speed Phase Accumulator for Direct Digital Frequency Synthesizer

<sup>1,2</sup>Salah Hasan Ibrahim, <sup>2</sup>Sawal Hamid Md. Ali and <sup>3</sup>Shabiul Islam

Corresponding Author: Salah Hasan Ibrahim, Faculty of Engineering, Diyala University, Republic of Iraq

#### ABSTRACT

This study presents 32-bit Phase Accumulator (PA) design, using the pipelining stages with modified Brent-kung (BK) adder. In this design, clock pulse division technique applied to reduce the number of the registers and thus reduce the power consumption. The new architecture of the 32-bit Phase accumulator with modified BK adder and clock pulse division technique, reduce the number of PA registers from 119-81 registers correspond to about 32% reduction. The comparing results of the proposed PA designs with the other designs, using the ALTERA software (Quartus 2 Cyclone 3) reveals that the PA designs with modified BK run about 27% faster and less delay compared with the previous works, as well as with the lowest number of registers and logic cells.

Key words: Phase accumulator, brent-kung adder, direct digital frequency synthesizer

# INTRODUCTION

The rapid development in the field of Radar and telecommunications requires a system capable of operating at a higher output frequency, precise frequency resolution and fast switching channel. Direct Digital Frequency Synthesizer (DDFS) is a system capable to meet these requirements and is increasingly attracting researchers to apply such system for telecommunications and Radar application. Phase accumulator (PA) is one of the main components in the DDFS system that gives huge impact to the performances that contain adder as one of its core elements in the architecture. Several techniques used to develop phase accumulator. Some of the solutions proposed to improve the speed and reduce the complexity by using parallel or pipelining design technique. The pipelining technique used to increase the throughput of the output frequency (Betowski and Beiu, 2003; Geng et al., 2010; Jensen, 2012; Ibrahim et al., 2012) but this leads to increase the power consumption and the chip area. The clock gating technique and two discrete clock drivers are used to drive two different flip flops applied in the phase accumulator design of DDFS to reduce the number of registers required in the pipeline without performance retraction by Yong Sin and Sung-Mo (2006), Chen et al. (2012) and Yoo et al. (2012), respectively. A high speed DDFS with low power pipelining parallel accumulator designed with 32-bit and 24-bit input (Yang et al., 2002; Chappell and McEwan, 2004; Horowitz and La Rue, 2005) based on pipelining parallel technique.

<sup>&</sup>lt;sup>1</sup>Faculty of Engineering, Diyala University, Republic of Iraq

<sup>&</sup>lt;sup>2</sup>Department of Electrical, Electronics and System Engineering,

<sup>&</sup>lt;sup>8</sup>Institute of Microengineering and Nanoelectronics, Universiti Kebangsaan Malaysia, 43600, UKM, Bangi, Malaysia

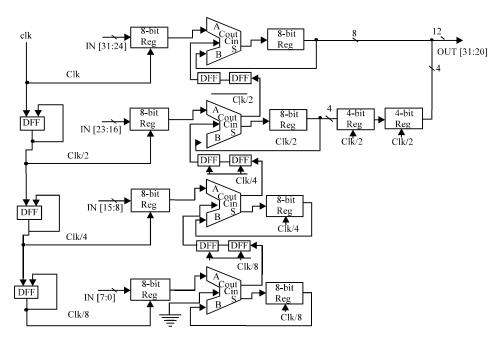

This study proposes a new design of 32-bit pipelined phase accumulator based on Brent-Kung (BK) Adder (Brent and Kung, 1982; Marso, 2008) and clock pulse division technique. Some modifications added to the BK adder structure in order to be used in a pipelining architecture. The PA based on 4 pipeline stages; each stage contains a modified 8-bit adder and an 8-bit register as a storage element. The carry-in of 8-bit BK adder in the first stage set as zero, while the carry-out connects to the carry-in of the next BK adder.

**Phase accumulator architecture:** The frequency resolution of a DDFS determined by the clock frequency  $(F_{dk})$  and the number of N input bit of the PA  $(F_{res} = F_{clk}/2^N)$ . The number of the pipeline stages depends on FCW bit and the number of bits in each stage.

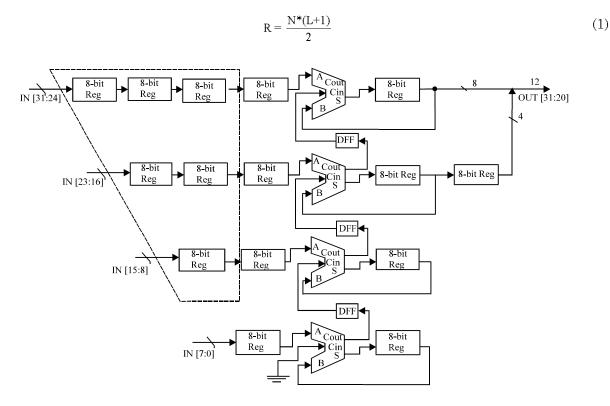

A large number of pipeline stages, increase the number of registers (Fig. 1), which leads to a higher power consumption. Therefore, in this design, a clock division technique used to reduce the number of registers while preserving the high speed operation. In this technique, D flip-flops (DFFs) used to connect between each row of the pipeline stages and control the FCW input registers in the stages. These registers clocked by the pipelined pulses with one clock cycle based on the dividing clock pulses. Doubling the DFFs between the pipelining rows, to overcome the doubling of clock frequency and reach the synchronization of the PA during the operating time. The new architecture of the 32-bit Phase accumulator with modified BK adder and clock pulse division technique shown in Fig. 2.

Considered the input bit of PA is N. The phase accumulator partitioned into L stages with B DFFs in each stage Fig. 1, a number of the pre skewing registers R are:

Fig. 1: Block diagram of 32-bit pipeline phase accumulator design

Fig. 2: Block diagram of 32-bit pipeline phase accumulator design based on 8-bit modifying Brent-Kung adder with clock division technique

Applying the clock pulsing division method for the proposed design, the calculation of pre skewing registers R becomes:

$$R = [N+3 (L-1)]$$

(2)

With the clock pulse division, the numbers of pre skewing registers reduced to a 48.7% reduction.

Pipelined PA starts counting only after (L+1) clock pulses, (L-number of pipeline stages). Applying the clock pulse division technique, the PA circuit operation passed with one clock pulse only and the output values appear after the second clock pulse.

With the clock pulse division technique, the numbers of PA registers reduced from 119-81 registers correspond to about 32% reduction (Fig. 1).

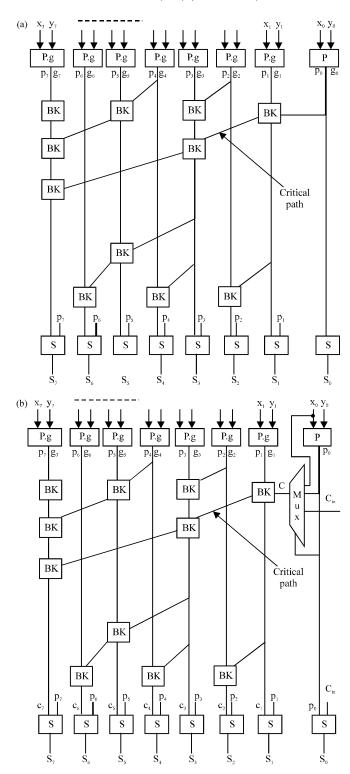

Brent-Kung adder is a fast adder and all the carries computed simultaneously through a binary tree of "BK" cells. BK cells consist of combinational logic gates and it computed as a sum of G and P (Bazargan, 2006):

$$BK = G + P \tag{3}$$

$$G = g'' + p'' \cdot g' \tag{4}$$

$$P = p''.p' \tag{5}$$

where, g'' g', p'' p' higher-lower generate and propagate function, respectively. The p-propagate function  $(p_i = x_i \oplus y_i)$  and g is a generate function  $(g_i = x_i \cdot y_i)$ .

Fig. 3(a-b): (a) Conventional Brent-Kung adder and (b) Modified Brent-Kung adder

To be able to use the BK adder in pipelining architecture, the adder modified by replacing the (p.g) block of the first bit Fig. 3a with an Exclusive OR gate (XOR) with the

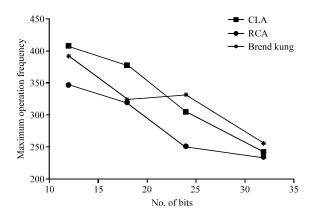

Fig. 4: Comparison result of maximum operating frequency  $(f_{\text{Max.}})$  for phase accumulator with Brent Kung, Carry Look-ahead (CLA) and Ripple Carry Adder (RCA)

$(X_0)$  input is multiplexed with carry input  $(C_{in})$  and carry out as the output of the multiplexer  $(C_1 = (p_0.C_{in}) + (X_0. p_0^-))$ , shown in Fig. 3b. Where:  $C_1$ -carry out,  $P_0$ -propagate function,  $C_{in}$ -Carry input and  $X_0$ -first bit input. The carry-out equations for each bit of the modified BK adder written below:

The sum and carry-out equations of the modified 8-bit BK adder shown in the Eq. 6-8:

$$S_0 = P_0 \oplus Cin \tag{6}$$

$$S_{(7,-1)} = P_{(7,-1)} \oplus C_{(7,-1)} \tag{7}$$

$$C_{\text{out}} = g_7 + P_7.C_7 \tag{8}$$

Several comparisons made for pipelining PA designs based on BK, CLA and RCA adder, including 12, 18, 24 and 32-bit. The comparison result shown in Fig. 4 and it shows that the proposed architecture is faster than conventional architectures, especially in PA with a large (8-bit) adder design.

#### EXPERIMENTAL RESULTS

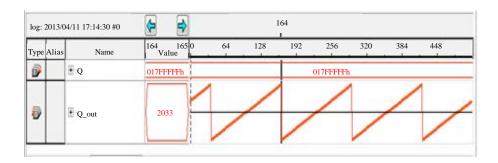

Proposed architecture successfully implemented on the Cyclone 3 FPGA platform, as shown in Fig. 5. The implementation shows that the Q output of the PA Increases steadily by FCW for every successive clock pulse, as long as the PA output  $Q = 2^{N-1}$ , then it resets back to zero. The Fig. 5 shows the output of the PA from the FPGA kit which appears as a saw tooth shape.

The performance of the proposed PA architecture compared with some previous works. For this purpose, the previous works re-designed and implemented on the same FPGA kit.

Table 1 shows the comparison results between the proposed phase accumulator and others previous works. The comparison shows that the proposed architecture performs significantly better compared to other architectures on a similar FPGA platform. The proposed architecture achieved

Fig. 5: Signal tap logic analyzer for PA with 32-bit BK adder implemented on Cyclone 3 FPGA Kit

Table 1: Comparison result between the proposed phase accumulator and others previous works

| Ref.               | Max. Freq f <sub>Max</sub> (MHZ) | Propag. Data delay Td (nano sec) | Logic cells                              | Registers |

|--------------------|----------------------------------|----------------------------------|------------------------------------------|-----------|

| Chen et al. (2012) | 83.56                            | 11.90                            | 113                                      | 86        |

| 32 bit PA with RCA | 136.50                           | 7.25                             | 127                                      | 113       |

| This work          | 268.31                           | 8.40                             | $20 + 4 \; \mathrm{LUT} \; \mathrm{LCs}$ | 82        |

higher operation frequency and smaller delay while keeping the lower number of components. The improved performances give an indication of bigger possibilities that can be achieved by the proposed design, when it's translated into integrated circuits.

#### CONCLUSION

A new architecture for high speed phase accumulator successfully designed and implemented. The new architecture of the 32-bit Phase accumulator with modified BK adder and clock pulse division technique, reduce the number of PA registers from 119 to 81 registers correspond to about 32% reduction. Comparison with the previous architecture on a similar FPGA platform shows that the proposed architecture runs about 27% faster and less delay compared with the previous works. All this is done, with a low number of components suggesting to lower power consumption.

### REFERENCES

Bazargan, K., 2006. EE 5324-VLSI design II: Adders. University of Minnesota. http://mountains.ece.umn.edu/~kia/Courses/EE5324/02-Adders/adders.pdf

Betowski, D.J. and V. Beiu, 2003. Considerations for phase accumulator design for direct digital frequency synthesizers. Proceedings of the International Conference on Neural Networks and Signal Processing, Volume 1. December 14-17, 2003, Nanjing, pp: 176-179.

Brent, R.P. and H.T. Kung, 1982. A regular layout for parallel adders. IEEE Trans. Comput., 100: 260-264.

Chappell, M. and A. McEwan, 2004. A low power high speed accumulator for DDFS applications. Proceedings of the International Symposium on Circuits and Systems, Volume 2, May 23-26, 2004, Vancouver, Canada, pp. II-797-II-800.

Chen, J., D. Wu, L. Zhou, J. Wu, Z. Jin and X. Liu, 2012. A 5.3-GHz 32-bit accumulator designed for direct digital frequency synthesizer. Chin. Sci. Bull., 57: 2480-2487.

Geng, X., F.F. Dai, J. Irwin and R.C. Jaeger, 2010. An 11-bit 8.6 GHz direct digital synthesizer MMIC with 10-bit segmented sine-weighted DAC. IEEE J. Solid-State Circ., 45: 300-313.

# Asian J. Sci. Res., 7 (1): 118-124, 2014

- Horowitz, I. and G.S. La Rue, 2005. Parallel phase accumulator architecture for DDFS. Proceedings of the IEEE Workshop on Microelectronics and Electron Devices, April 15, 2005, Boise, ID., USA., pp. 63-66.

- Ibrahim, S.H., S.H.M. Ali and M. Islam, 2012. High speed direct digital frequency synthesizer with pipelining phase accumulator based on Brent-Kung adder. Proceedings of the 10th IEEE International Conference on Semiconductor Electronics, September 19-21, 2012, Kuala Lumpur, Malaysia, pp. 547-550.

- Jensen, B.S., 2012. Twelve-bit 20-GHz reduced size pipeline accumulator in 0.25 [micro sign]m SiGe:C technology for direct digital synthesiser applications. IET Circ. Devices Syst., 6: 19-27.

- Marso, L., 2008. Brent-Kung fast adder dscription, simulation and formal verification using lava. Proceedings of the Argentine School of Micro-Nanoelectronics, Technology and Applications, September 18-19, 2008, Buenos Aires, Argentina, pp. 111-114.

- Yang, B.D., L.S. Kim and H.K. Yu, 2002. A high speed direct digital frequency synthesizer using a low power pipelined parallel accumulator. Proceedings of the IEEE International Symposium on Circuits and Systems, Volume 5, May 26-29, 2002, Scottsdale, Arizona, USA., pp: V-373-V-376.

- Yong Sin, K. and K. Sung-Mo, 2006. A high speed low-power accumulator for direct digital frequency synthesizer. Proceedings of the International Symposium Microwave MTT-S Digest, June 11-16, 2006, San Francisco, CA., pp. 502-505.

- Yoo, T., S.J. Cho, J.W. Lee and K.H. Baek, 2012. Low-power fast-update pipelined phase accumulator for CML-based high-speed CMOS DDFSs. Electron. Lett., 48: 1102-1104.