http://ansinet.com/itj

ISSN 1812-5638

# INFORMATION TECHNOLOGY JOURNAL

Asian Network for Scientific Information 308 Lasani Town, Sargodha Road, Faisalabad - Pakistan

# Reliability Evaluation of Collaborative Product Design Process Considering Redesigning Activities

Tao Yang and Yu Yang State Key Lab of Mechanical Transmission, Chongqing University, 400030, Chongqing, China

**Abstract:** During the product design phase, due to various factors and random failures, input materials processed might be defective and would be less than input amount. In order to increase the output, defective products are usually formed as a reverse product flow and redesigned. However, these activities would cause an increment of the design capability and processing time for the design entities. The objective of this research is to propose a reliability evaluation model and solution method that would determine the reliability for the product design phase with reverse logistics product re-designing activities. The evaluation model contains design capability and processing time two aspects and the whole system reliability can be derived afterwards. Finally, a case study is presented to illustrate the usefulness of the proposed approach.

**Key words:** Product design phase, reliability, redesigning activities

### INTRODUCTION

Product design phase is one of the most important processes and as much as 75% of the cost of a product is being committed (Hsu and Irene, 1998). Therefore, it is a crucial issue to measure the capability of a Product Design Phase (PDP) and determine whether it can satisfy customers' orders or not. The reliability analysis is one of the essential roles to be researched. In recently years, a consistent growing number of studies have been published (Golomski, 1995; Chin et al., 2008; Liang et al., 2008; Sanchez and Rong, 2011; Rathod et al., 2012; Cardoso et al., 2013). However, the reliability analysis of the PDP is still far from being totally studied. The product manufacturing network is composed by a number of production activities. It contains two kinds of logistic activities, Forward Logistics (FL) and Reverse Logistics (RL). During the design phase, in order to ensure quick delivery of good quality products, these defects products are usually repaired or reworked and formed a reverse product flow (Lin and Chang, 2012). Once it occurs, the processing capability and time of the related design entities will increased and may cause a huge lost if it was not well-considered. So, how to evaluate the products design phase with re-designing activities has becoming an important issue.

# MODEL CONSTRUCTION

Assuming that the product design work A can be finished by one design entity  $1^{\#}$ , in order to produce

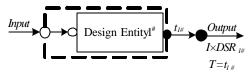

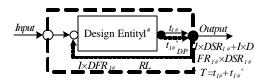

sufficient products for the customers' demand d under the exists of the DSR<sub>1#</sub> and complete the product design work under the delivery time T'. Firstly, the amount of input materials (I) should more than the output quantity (O). Then, calculate the outputs (O). The outputs consist of different types of products: (1) The input and output flow without the existence of RL activities, as shown in Fig. 1; (2) The input and output flow with the RL activity, as shown in Fig. 2. From the above two conditions, we can get that the design processing time of case (2) is obviously more than case (1). Suppose that the design work can be finished under the given time T'. We attempt to obtain the relationship between I, O and d fulfilling O>d and T<T'. For the simplest case with only one design entity, once the value of DSR and output (O) are determined, the input (I) and (T) can be easily obtained.

Fig. 1: Design work without RL activities

Fig. 2: Design work with RL activity

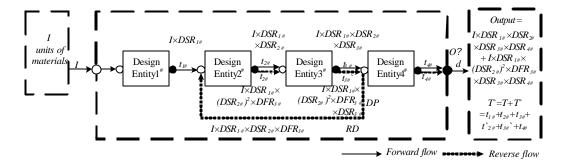

Fig. 3: Product design with four design entities

Take the PDP with four design entities for example. In Fig. 3, we can see there are I units of raw materials entering design entity 1# and I×DSR<sub>1#</sub> units of WIDPs outputting from design entity 1#, meanwhile, there are  $t_{1#}$  units of time were consumed during this phase. Afterwards, I×ESR<sub>1#</sub> units of WIDPs entering design entity 2# and I×DSR<sub>1#</sub>×DSR<sub>2#</sub> units of WIDPs outputting from design entity 2#. Still, there are  $t_{2\#}$  units of time were consumed during this design phase. Without considering the RL activities,  $O = I \times DSR_{1\#} \times DSR_{2\#} \times DSR_{3\#} \times DSR_{4\#}$  units of successful design product outputting from design entity 4#. Simultaneously, there are  $\sum t_{1\#} (i = 1, 2, 3, 4)$  units of time were consumed. In order to satisfy the customer's demand O and the demanding delivery time T', the input I and  $t_{1\#}$  should be meeting the following two objectives:

Objective function 1:

**Constraints:** Equation 2 tries to guarantee that do not exceed the maximal capacity that each design entity can provide:

$$\begin{cases} I \leq C_{1\#} \\ I \times DSR_{1\#} \leq C_{2\#} \\ I \times DSR_{1\#} \times DSR_{2\#} \leq C_{3\#} \\ I \times DSR_{1\#} \times DSR_{2\#} \times DSR_{3\#} \leq C_{4\#} \end{cases}$$

$$(2)$$

Objective function 2:

$$\sum_{i=1}^{4} t_{i\#} \le T' \tag{3}$$

**Constraints:** Equation 4 tries to guarantee that do not exceed the product processing time that each design entity predetermined:

$$t_{1\#} \le DT_{1\#}, t_{2\#} \le DT_{2\#}, t_{3\#} \le DT_{3\#}, t_{3\#} \le DT_{4\#}$$

(4)

The above analysis is about product flow without RL activities. In reality, RL activities are essential for satisfying customers' demands and reducing production cost. Consider the DPs outputting from design entity3# are re-designed starting from design entity2#. Here:

- f<sup>(F)</sup> represents the FL activities

- f<sub>i#</sub><sup>(F)</sup> indicates the forward input flow processed by each design entity

- f<sup>(R)</sup> represents the RL activities. We use the graphical technique revised the product design network as shown in Fig. 3. In order to satisfy the customer's demand O and T, the input I and t<sub>i#</sub> should be meet the following two objectives

Objective function 3:

$$I \ge d / \left[ \prod_{i=1}^{4} DSR_{i\#} \left( 1 + DSR_{2\#} DFR_{3\#} \right) \right]$$

(5)

**Constraints:** Equation 6 tries to guarantee that do not exceed the maximal capacity that each design entity can provide:

$$\mathbf{f}_{i\#}^{(F)} + \mathbf{f}_{i\#}^{(R|3^{\#},3^{\#}-2^{\#})} \le \mathbf{C}_{i\#} \tag{6}$$

Objective function 4:

$$\sum_{i=1}^{4} (t_{i\#} + t'_{i\#}) \le T' \tag{7}$$

**Constraints:** Equation 8 tries to guarantee that do not exceed the product process time that each design entity pre-determined:

$$xt_{i\#} + t'_{i\#} \le DT_{i\#} \tag{8}$$

Based on the above examples, we can generalize the objective function 3 and 4. Assume that there are n design entities in the PDP, each design entity have an equal

$DSR_{\#} = DSR$  and given demand d and delivery time T`, the relationship between I, O, d, DSR, n and T` are as follows:

$$\mathbf{f}_{i,\mu}^{(F)} = \mathbf{I} \times \mathbf{DSR}^{i-1} \tag{9}$$

$$f_{i\#}^{(F)} = I \times \prod_{t=1}^{n-1} DSR_{t\#}$$

(10)

$$\mathbf{f}_{i\#}^{(R|f',f'-k'')} = \mathbf{I} \times \mathbf{DSR}^{i+j-k+l} \mathbf{DFR}$$

(11)

$$\mathbf{f}_{i\#}^{(R_j)^{H_j,H_k,H_j}} = \mathbf{I} \times \prod_{t=1}^{j-1} \mathbf{DSR}_{t\#} \mathbf{DFR}_j \times \prod_{t=k}^{i-1} \mathbf{DSR}_t \tag{12}$$

Equations 9, 10 and 11, 12 are all represent the input flows that would be designed for design entity i\*, especially, Eq. 9,10 is for the FL activities while Eq. 11, 12 is for the RL activities. The generalized objective function (3\*) and (4\*) are as below:

Objective function 3\*:

$$I \ge d/(DSR^n + DSR^{n+j-k}DFR)$$

(13)

$$I \geq d \! \left/ \! \left( \prod_{t=1}^{n} \mathbf{DSR}_{t\#} + \prod_{t=1}^{j-1} \mathbf{DSR}_{t\#} \mathbf{DFR}_{j} \times \prod_{t=k}^{n} \mathbf{DSR}_{t} \right. \right) \tag{14} \right.$$

**Constraints:** Equation 15 tries to guarantee that do not exceed the maximal capacity  $C_{i\#}$  that each entity can provide:

$$\mathbf{f}_{:u}^{(F)} + \mathbf{f}_{:u}^{(R|j^{\#},j^{\#}-k^{\#})} \le C_{:u} \tag{15}$$

Objective function 4\*:

$$\sum_{i=1}^{n} \left( t_{i\#} + t'_{i\#} \right) \le T' \tag{16}$$

**Constraints:** Equation 17 tries to guarantee that do not exceed the product process time that each design entity pre-determined:

$$t_{nil} + t'_{nil} \le DT_{nil} \tag{17}$$

According to the above Eq. 9-14, we can get the value of parameters I and C<sub>i</sub>. In this study, we study the problem where the product design processing times follow exponential distributions (Cai and Zhou, 2000). Consider the following case: A number of inputs /WIDPs are to be sequential processed non-preemptively on each

design entity and the processing times are independently with each other and exponentially distributed with mean  $\sigma_{n\#}$ . The probability density function of  $t_i$  is:

$$f(t_i) = \begin{cases} \sigma_i e^{-\sigma_i t_i} & \text{if } t \ge 0\\ 0 & \text{if } t < 0 \end{cases}$$

(18)

Mean product design processing time is  $1/\sigma_i$  units of time. So, the expected product designing processing time  $ti = t_{i\#t'\#}$  for design entity  $i^\#$  is:

$$\mathbf{t}_{i} = \left(\mathbf{f}_{i\#}^{(F)} + \mathbf{f}_{i\#}^{(R|f',j''-k'')}\right) \mathbf{E}\left(\mathbf{t}_{i}\right) \tag{19}$$

## RELIABILITY EVALUATION

Given the customer's demand d,  $DSR_{i\#}$  and the design processing time distributions  $f(t_i)$  (i=1,2,3,...,n) for each design entity, according to assumption 4 that for each design entity i<sup>#</sup> the values of the working capacity  $y_i$  and design processing time  $x_i$  are random variables. In order to satisfy the customer's demand d under the amount time T', we should follow the constraint (20) as below:

$$\begin{cases} \mathbf{y}_{i} \ge \mathbf{I}_{i} \\ \mathbf{t}_{i} \le \left(\mathbf{x}_{i} | \mathbf{y}_{i}\right) \end{cases} \tag{20}$$

Where:

$$\boldsymbol{y}_{i} \leq \boldsymbol{C}_{i\#}, \, \boldsymbol{y}_{i} \in \boldsymbol{N}^{+}, \, \boldsymbol{x}_{i} \leq \boldsymbol{D}\boldsymbol{T}_{i\#}, \, \sum_{i=1}^{n} \boldsymbol{x}_{i} \leq \boldsymbol{T}'$$

$i=1,\,2,\,3\,\ldots,\,n,\,(x_i|y_i)$  means the processing time  $x_i$  under  $y_i$  units of materials are processed.

We use  $R_1$  represents the product design reliability of the design entity  $1^{\#}$ . For the purpose of reaching the customer demand d, design entity  $1^{\#}$  should processed at least  $y_i$ =I units of raw materials, the probability of design entity  $1^{\#}$  process  $y_i$  units raw materials under its design capability is denoted as  $P_{\text{Cal}}$ , that is  $P_{\text{cal}} = P(y_{\text{IsII}})$ . Besides,  $P_{\text{TiI}}$  represents the probability of design entity  $1^{\#}$  process  $y_i$  units raw materials under the processing time  $x_i$ , that is,  $P_{\text{tiI}} = P(t_i \le (x_i, y_i))$ . So, reliability of the design entity  $1^{\#}$ :

$$R_1 = P(y_1 y_1 \ge I_1) \times P(t_1 \le (x_1 | y_1)) = P_{Ca1 \times} P_{Ti1}$$

(21)

Using  $R_d$  represents the reliability of the whole product design work:

$$R_{d} = \prod_{i=1}^{n} R_{i} \tag{22}$$

#### COMPUTATIONAL STUDY

In this section, we take the cermet product surface design as an example for the reliability analysis of the product design phase with RL activities. The design phase consists of four steps as below:

- **Step 1:** Surface treatment of the cermet

- Step 2: Add a surface treatment agent

- Step 3: Pattern decoration

- **Step 4:**High-temperature treatment with 1400°C-1700.

During the design process, design works were assigned to four design entities in Fig 3 that has to satisfy the customer demand d=30 within 5 dates. The DP output from Step 3 returned to Step 2 for re-designing, the design capacity distribution of each design entity is shown in Table 1. We can calculate out the parameters  $I_i$  and  $t_i$  as follows:

Table 1: Capacity distribution of each design entity

| Design entity | Capability | $P_{Cai}$ | Design entity | Capability | $P_{Cai}$ |

|---------------|------------|-----------|---------------|------------|-----------|

| 1#            | 0          | 0.001     | 3#            | 0          | 0.005     |

| DSR = 0.95    |            |           | DSR = 0.95    | 7          | 0.005     |

|               | 12         | 0.01      |               | 14         | 0.01      |

|               | 24         | 0.02      |               | 21         | 0.01      |

|               | 36         | 0.969     |               | 28         | 0.015     |

|               |            |           |               | 35         | 0.955     |

| 2#            | 0          | 0.001     | 4#            | 0          | 0.001     |

| DSR = 0.95    | 7          | 0.005     | DSR = 0.95    | 8          | 0.005     |

|               | 14         | 0.005     |               | 16         | 0.005     |

|               | 21         | 0.01      |               | 24         | 0.01      |

|               | 28         | 0.015     |               | 32         | 0.979     |

|               | 35         | 0.964     |               |            |           |

Table 2: Results of step1 and step2

| Design entity                |         |         |         |         |         |

|------------------------------|---------|---------|---------|---------|---------|

| Input flow                   |         | 1#      | 2#      | 3#      | 4#      |

| $f_{i\not \!\! F}^{(F)}$     | (1)     | 35.16   | 33.40   | 31.73   | 30.15   |

| $f_{i\#}^{(R 3\#, 3\#-2\#)}$ | (2)     | 0       | 1.59    | 1.51    | 1.43    |

| $I_i$                        | (1)+(2) | [35.16] | [34.99] | [33.24] | [31.57] |

| t <sub>i</sub> (min)         | 1384.6  | 1093.8  | 1093.8  | 1391.3  |         |

Table 3: Time distribution for each design entity's processing

|                | Processing |           | Design         | Processing |           |

|----------------|------------|-----------|----------------|------------|-----------|

| Design entity  | time       | $PT_{ii}$ | entity         | time       | $PT_{ii}$ |

| 1#             | 0          | 0.001     | 3#             | 0          | 0.001     |

| DSR = 0.95     | 200        | 0.001     | DSR = 0.95     | 100        | 0.001     |

| $I_1 = 36$     | 400        | 0.005     | $I_3 = 35$     | 300        | 0.002     |

| $t_1 = 1384.6$ | 600        | 0.005     | $t_3 = 1093.8$ | 500        | 0.003     |

|                | 800        | 0.01      |                | 700        | 0.015     |

|                | 1000       | 0.015     |                | 900        | 0.02      |

|                | 1200       | 0.015     |                | 1100       | 0.958     |

|                | 1400       | 0.948     |                |            |           |

| 2#             | 0          | 0.001     |                | 0          | 0.001     |

| DSR = 0.95     | 100        | 0.001     | 4#             | 200        | 0.002     |

| $I_2 = 35$     | 300        | 0.002     | DSR = 0.95     | 400        | 0.002     |

| $t_2 = 1093.8$ | 500        | 0.002     | $L_1 = 32$     | 600        | 0.01      |

|                | 700        | 0.01      | $t_4 = 1391.3$ | 800        | 0.01      |

|                | 900        | 0.015     |                | 1000       | 0.015     |

|                | 1100       | 0.969     |                | 1200       | 0.015     |

|                |            |           |                | 1400       | 0.945     |

- Step 1: Determine the input amount of raw materials

I and the amount of input flow I<sub>i</sub> for each design entity. However, the eventually exact amount of output products would be an integer, so, we can obtain (I<sub>1</sub>, I<sub>2</sub>, I<sub>3</sub>, I<sub>4</sub>) = (36, 35, 35, 32)

- **Step 2:** Determine the time parameters  $t_i$  for each design entity, the results of the amount of each product design entity input flow I,  $I_i$  and  $t_i$  are shown in Table 2

- Step 3: In order to satisfy the customer demands from product quantity (d) and delivery time (T') two aspects, we will not only evaluate the design capability of each design entity which was required for meeting the customer needs for products, but also evaluate whether these products can be completed in a given time or not. The product design processing time distribution P<sub>Tii</sub> = P(t<sub>is(xi|yi)sDTi#</sub>) of each design entity is shown in Table 3

- Step 4: Based on the above obtains, according to Eq. 21 and 22, the cermet product design process reliability R<sub>d</sub> is derived as follows:

$$\begin{split} R_1 &= P(y_1 \! \ge \! 36) \! \times \! P(1400 \! \le \! (x_1|36) \! \le \! DT_{i\#}) \; P_{cal} \! \times \! P_{Ti1} \! = \\ 0.969 \! \times \! 0.948 &= 0.919 \\ R_2 &= 0.921 \, ; \; R_3 = 0.924 \; ; \; R_4 = 0.925 \\ R_4 \! = \! R_1 \! \times \! R_2 \! \times \! R_3 \! \times \! R_4 = 0.7234 \end{split}$$

# CONCLUSION

In this study, it has proposed a reliability evaluation model for the product design phase with forward and reverse product flows where design capability and the processing time sfor each design entity were explored under a certain amount of customers products demand and product delivery time context. The model application shows the reverse logistics during design process may result in an increment of the design capacity and processing time for each design entity, whether the design capability and product processing ability can satisfies the demand and delivery time becomes a key problem to the whole design system reliability. Based on the analysis, the manager could conduct the sensitivity analysis to investigate the most important design entity in design phase and to improve the design work to be more reliable.

#### ACKNOWLEDGMENTS

This research is funded by the National Nature Science Foundation of China (No. 71071173; 71301176).

### REFERENCES

- Cai, X. and X. Zhou, 2000. Asymmetric earliness and tardiness scheduling with exponential processing times on an unreliable machine. Ann. Oper. Res., 98: 313-331.

- Cardoso, S.R., P. Barbosa, F.D. Ana Paula and S. Relvas, 2013. Design and planning of supply chains with integration of reverse logistics activities under demand uncertainty. Eur. J. Oper. Res., 226: 436-451.

- Chin, K.S., A. Chan and J.B. Yang, 2008. Development of a fuzzy FMEA based product design system. Int. J. Adv. Manuf. Technol., 36: 633-649.

- Golomski, W.A., 1995. Reliability and quality in design. IEEE Trans. Reliab., 44: 216-219.

- Hsu, W. and I.M.Y. Irene, 1998. Current research in the conceptual design of mechanical products. Comput.-Aided Design, 30: 377-389.

- Liang, J.H., P.M. Zissimos and T. Jian, 2008. A single-Loop method for reliability-based design optimization. Int. J. Prod. Dev., 5: 76-92.

- Lin, Y.K. and P.C. Chang, 2012. Evaluate the system reliability for a manufacturing network with reworking actions. Reliab. Eng. Syst. Safe, 106: 127-137.

- Rathod, V.Y., P.R. Om and A.J. Rakesh, 2012. Reliability based design optimization considering probabilistic degradation behavior. Qual. Reliab. Eng. Int., 28: 911-923.

- Sanchez, L.M. and P. Rong, 2011. An enhanced parenting process: Predicting reliability in product's design phase. Quality Eng., 23: 378-387.