# Research Journal of Information Technology

ISSN 1815-7432

Research Journal of Information Technology 6 (3): 166-177, 2014 ISSN 1815-7432 / DOI: 10.3923/rjit.2014.166.177 © 2014 Academic Journals Inc.

# Analysis of Multi Level Current Source Inverter: A Critic Based on Various PWM Control Strategies

R. Balasubramanian, K. Parkavi Kathirvelu and Rengarajan Amirtharajan School of Electrical and Electronics Engineering, SASTRA University, India

Corresponding Author: R. Balasubramanian, School of Electrical and Electronics Engineering, SASTRA University, India

### ABSTRACT

DC/AC power converters are very much useful to provide ac output from DC power supply. Based on their operation, these converters find their way in lot of applications such as Flexible AC Transmission System (FACTS), Uninterruptible Power Supply (UPS), HVDC Transmission System etc. These converters are often classified into voltage source and current source inverters. In these, multi-level configuration is common for both converters which are suitable for high power applications. This study explains a different multi-level current source inverter configuration with various PWM control strategies. The operation and analysis of the proposed converter with control strategies are examined through PSIM and MATLAB simulation. The result shows the variation in the output Total Harmonic Distortion (THD) for different control methods.

**Key words:** Multi level current source inverter, total harmonic distortion, multi carrier modulation, unipolar carrier overlapping PWM, bipolar carrier overlapping PWM, current source inverter

### INTRODUCTION

Nowadays usage of DC/AC power converters have been increased vastly, because of its suitability in connecting non conventional energy sources like photo voltaic and fuel cells into electrical grid (Lai and Peng, 1996; Balasubramanian et al., 2014a; Kathirvelu et al., 2014). The DC/AC converters plays vital role in DC microgrid system (Arthishri et al., 2014). In general DC/AC power converter topologies are generally classified as Voltage Source Inverter (VSI) and Current Source Inverter (CSI). Recently VSI has been studied more than CSI in literature, however CSI are mostly preferred where boosting capabilities are required. The CSI has lot of advantages compared to VSI such as Low switching dv/dt, high short circuit ratio, Lagging VAr compensation and also used in adjustable motor drives Ramezani (2010), Balasubramanian et al. (2014b) and Bashi et al. (2008). Bulky inductors are present at the input side of the CSI to have smooth DC current and also protect the circuit from over current.

In CSI, multi level configuration is considered because the output can be stepped up to higher voltages levels even when the input current is very low. Moreover, these multi level CSI possess lots of benefits like lower switching losses, low electromagnetic interference (EMI), high quality power output and higher output voltage, improved power quality etc.

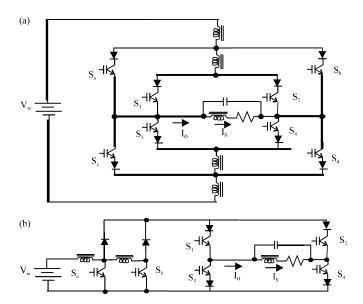

Multi level CSI can be divided into two types namely embedded configuration and two stage configurations as shown in Fig. 1. In this study a different multi level configuration namely paralleled configuration is analysed which is more prominent than other topology and requires

Fig. 1(a-b): (a) Embedded converter and (b) Two stage converter

single power supply with reduced number of semiconductor switches to get higher current levels at the output (Farahani, 2008; Vazquez et al., 2010; Wu et al., 2013; Mailah et al., 2008). The main drawback of CSI is discrete diodes which are connected in series with semiconductor switches reduces the efficiency. Due to the emerging of reverse-blocking IGBTs, the series diodes may not be needed in coming future. The current source inverters have lot of merits compare to the voltage source converters and also have inherent short circuit protection capability.

This study elaborates the working of seven levels CSI which uses IGBTs as semiconductor switches. Here eight switches are required to get the seven level output and also the output has low harmonic content. The performance of the converter is analysed and verified using computer simulation (PSIM, MATLAB) for various control techniques and also the Total Harmonic Distortion (THD) is calculated. In this study modified converter topology is explained and its supremacy is shown with the help of comparison with novel converter topology. Its performance is analysed with different control techniques such as multicarrier modulation, unipolar carrier PWM techniques and bipolar carrier overlapping PWM techniques. Finally THD is calculated for all the methods and the results were compared.

# METHODOLOGY

Current source inverters are used in the applications where boosting capabilities are required. One of the applications is adjustable motor drive and another is photovoltaic and wind systems. The proposed configuration reveals that, CSIs are joined together in parallel manner to get the desired multi level output. These converters can work efficiently even though voltage sag problem occur at the input voltage because of its boosting capabilities.

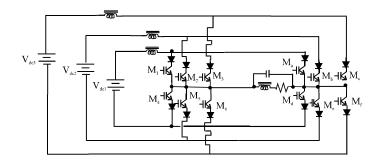

**Paralleled MLCSI:** In this study, three CSIs are connected in parallel to get the required seven level output. Figure 2 shows the traditional seven level circuit having three distinct voltage sources. If the values of the voltage sources are identical then the traditional circuit can be modified as shown in Fig. 3. Higher levels can be obtained by just adding

Res. J. Inform. Technol., 6 (3): 166-177, 2014

Fig. 2: Traditional seven level converter

Fig. 3: Modified converter

Table 1: No. of switches required for various levels

| No. of sources | Switches required | No. of levels |

|----------------|-------------------|---------------|

| 1              | 4                 | 3             |

| 1              | 6                 | 5             |

| 1              | 8                 | 7             |

| 1              | 10                | 9             |

| 1              | 12                | 11            |

| 1              | 14                | 13            |

two switches and an inductor with traditional circuit. Table 1 gives the information about the number of switches required to get the appropriate output current level.

Converter description: The converter analysed in this study has almost ripple free input current and assumed as constant because of large inductors present in the input side. In the modified converter as shown in Fig. 3 switches M1, M2, M3 and Md are triggered sequentially to get the seven level output at the positive side. Similarly Ma, Mb, Mc and M4 are triggered to get the negative side output. Here M1 and Ma are triggered exactly at opposite phase angles and this is same for other switches also. Table 2 gives the possible switching states of the converter. Explanation about the working of various levels as follows:

**Zero level:** For Zero level either all the switches M1, M2, M3, M4 are either turned ON or at OFF condition.

**Positive level:** In order to get a positive current level at the output, only one switch is turned ON at the positive side. The possible switching combinations for this level are given below:

- M1 is maintained ON, M2 and M3 are turned OFF

- M2 is maintained ON, M1 and M3 are turned OFF

- M3 is maintained ON, M1 and M2 are turned OFF

**Double positive level:** In this level magnitude of the output current is twice the magnitude of previous level. Here two switches at the positive side are turned ON and other possible combinations are shown in Table 2.

**Triple positive level:** In this level magnitude of the output current is thrice the magnitude of positive level. All the switches at the positive side are turned ON except M4 for this level.

**Negative level:** This level is exactly opposite to positive current level and also current flow direction is reversed. At positive side except switch M1 the remaining switches are maintained ON to get the first negative level and other possible switching combinations are shown in Table 2.

**Double negative level:** In order to get this level two switches in the positive side are maintained in OFF condition except M4. The magnitude of output current is twice the magnitude of the previous level.

**Triple negative level:** In this level magnitude of the output current is thrice the magnitude of the negative level. To achieve this level at the positive side all switches are kept in OFF condition except M4.

Control techniques: The control strategies play a major role in the functioning of the converter to get accurate AC output. Behaviour of the converter can be tuned efficiently with the help of modulation strategies (Boost and Ziogas, 1988; Chen et al., 2013; McGrath and Holmes, 2002;

Table 2: Possible switching combinations of the converter

| Output current        | M1 | M2 | М3 | M4 |

|-----------------------|----|----|----|----|

| Zero level            | SN | SN | SN | SN |

|                       | SF | SF | SF | SF |

| Positive level        | SN | SF | SF | SF |

|                       | SF | SN | SF | SF |

|                       | SF | SF | SN | SF |

| Double positive level | SN | SN | SF | SF |

|                       | SF | SN | SN | SF |

|                       | SN | SF | SN | SF |

| Triple positive level | SN | SN | SN | SF |

| Negative level        | SF | SN | SN | SN |

|                       | SN | SF | SN | SN |

|                       | SN | SN | SF | SN |

| Double negative level | SN | SF | SN | SN |

|                       | SF | SN | SF | SN |

|                       | SF | SF | SN | SN |

| Triple negative level | SF | SF | SF | SN |

SN: Switch on, SF: Switch off

He et al., 2014; Gholami and Seifi, 2012). In this study switching control is based on pulse width modulation technique however multi carriers are used. The modulation index is given by the definition as:

$$M = \frac{Vp}{Vt}$$

where, Vp is the reference amplitude and Vt is the carrier signal peak value. In a customary sinusoidal Pulse Width Modulation, at all times the carrier signal is compared with the reference; here, multiple carriers are used to generate PWM.

The PWM control strategies used to analyse the converter are as follows:

- Multi Carrier Modulation (MCM)

- Unipolar carrier PWM techniques

- Bipolar carrier overlapping PWM technique

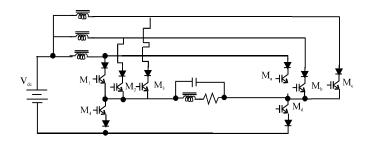

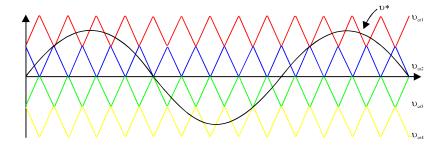

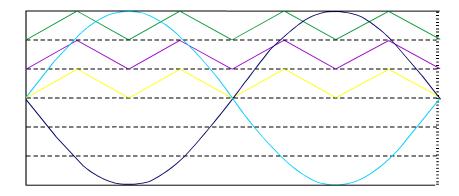

Multi Carrier Modulation (MCM): In multi carrier modulation strategy (H-1) carriers are required exactly to obtain H levels at the output. High frequency triangular carrier waveforms are compared with sinusoidal reference for generating the switching pulses of the switches as shown in Fig. 4.

This MCM technique can be divided into Level shifted PWM (LSPWM) and Phase shifted PWM (PSPWM). Of these the LSPWM can be further branched into the following:

- Alternative Phase Opposition Disposition (APOD)

- Phase Disposition (PD)

- Phase Opposition Disposition (POD)

Level shifted PWM is natural extension of bipolar PWM for multi level inverters. Bipolar PWM compares the reference signal to one carrier signal to decide between two different voltage levels, they are the negative and positive bus bars of CSI. The H-1 carriers are needed for a multi level inverter by generalizing the above idea. These PWM carriers are arranged in vertical shifts instead

Fig. 4: Traditional MCM waveform

Res. J. Inform. Technol., 6 (3): 166-177, 2014

Fig. 5: APOD MCM with carrier variation

Fig. 6: PD MCM with carrier variation

of the phase-shift utilized in PS-PWM. Two voltage levels are used to set each carrier between them; so that it has the name of level shifted pulse width modulation. The usual bipolar PWM's principle can be applied because of every carrier is having two levels. The corresponding levels are generated applying the control signal to the appropriate semiconductors by taking into account of bipolar PWM principle.

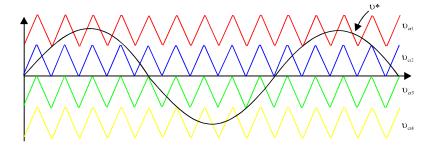

The Fig. 5 and 6 illustrate these PWM techniques. Phase shifted PWM are normally used in the flying capacitor type multilevel inverters.

Figure 5 indicates that carriers present above the reference have phase variation by 180 with respect to the carriers below reference line:

- Phase disposition MCM: In phase disposition multi carrier modulation PWM all carrier bands are in phase with respect to origin. Figure 6 indicates the PDMCM with carrier variation

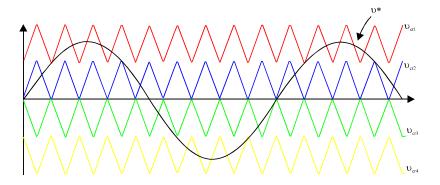

- **Phase opposition disposition MCM:** Figure 7 shows the Phase Opposition Disposition (POD) MCM carrier bands at positive side are out of phase by 180 with negative side

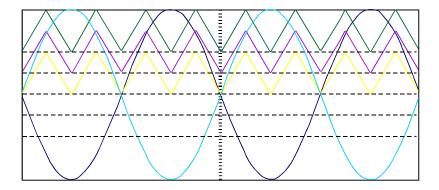

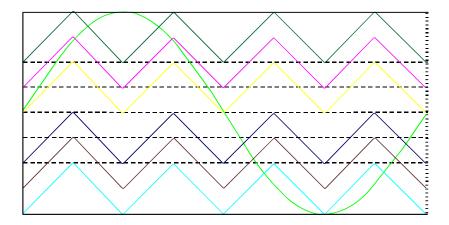

**Unipolar PWM techniques:** As the name portrait that the carrier bands are exist only at upper or above the origin only. In this PWM technique two sine waves are used as reference signal and are phase varied by 180° for producing pulses at both half cycles to ignite the switches. In these method (H-1)/2 carriers are used to get H levels further it is classified as unipolar carrier overlapping PWM (UCOPWM) and Unipolar sub harmonic PWM.

Unipolar carrier overlapping PWM: The UCOPWM has three merged carriers are employed to get the seven level output. Gating signals are obtained by comparing two

Res. J. Inform. Technol., 6 (3): 166-177, 2014

Fig. 7: POD MCM with carrier variation

Fig. 8: Carrier arrangements in UCOPWM

sinusoids with three merged carriers as shown in Fig. 8. In this PWM technique all the carriers are merged in positive half cycle of the reference signal

• Unipolar sub harmonic PWM: This strategy is similar to multi carrier modulation and Fig. 9 shows the carrier arrangements in USHPWM

**Bipolar carrier overlapping PWM:** This topology finds a way that it is the combination of both UCOPWM and MCM. As the name indicates that in this method carriers are overlapped and also present in both regions as like MCM. In this method (H-1) carriers are needed to get H level output as shown in Fig. 10. This modulation technique uses two carrier signals with bipolar arrangement.

# RESULTS AND DISUSSION

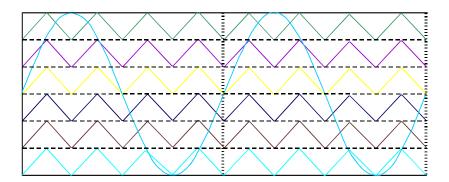

The reliability of the proposed control techniques and the operation of the seven levels CSI have been observed with the help of computer simulation using PSIM and also MATLAB. A seven level current source inverter with the load parameters shown in the table is simulated with various PWM control strategies and the result shows the variation in the output THD. The voltage and current waveform obtained across the load from simulation shows that it has less distortion. In simulation all the parameters of the proposed system are assumed to be linear and by keeping the load as constant the PWM control method alone changed. Simulation parameters are shown in Table 3.

Res. J. Inform. Technol., 6 (3): 166-177, 2014

Fig. 9: Carrier arrangements in USHPWM

Fig. 10: Carrier arrangements in BCOPWM

Table 3: Simulation parameters

| Parameters          | Values                                 |

|---------------------|----------------------------------------|

| Smoothing inductors | 400 mH                                 |

| Input voltage       | 100 V                                  |

| Switching frequency | 5-10 kHz                               |

| Filter capacitor    | 20 μF                                  |

| Load                | $R = 10 \Omega$ , $L = 500 \text{ mH}$ |

| Output voltage      | 300 V                                  |

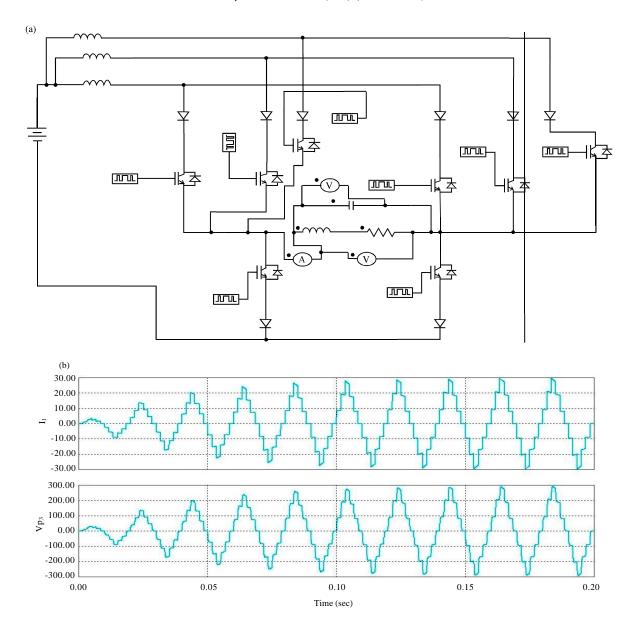

Figure 11a shows the proposed seven levels current source inverter as a parallel combination of two level current source inverters. Figure 11b shows the seven level voltage and current output. THD for the proposed system is analysed with various PWM control techniques. As these figures show, these control methods can be successfully applied for the proposed CSI topology. The lower order harmonics can be mitigated by increasing the number of levels as well as the switching modulation strategies.

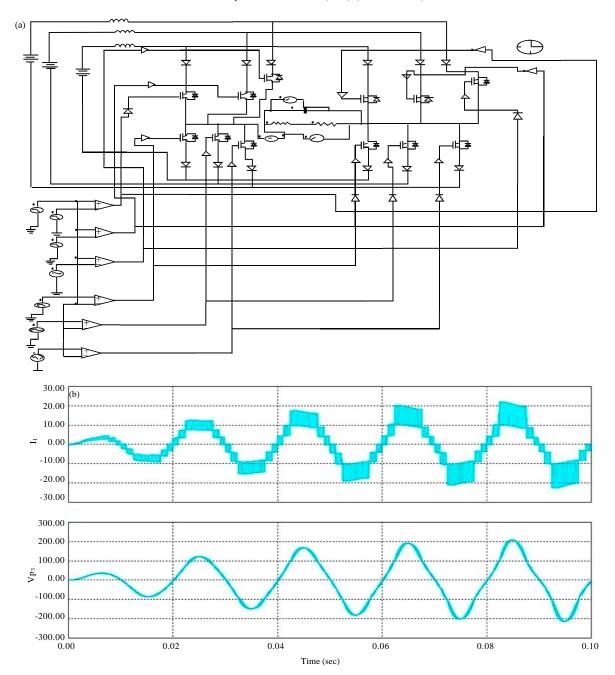

Figure 12a shows the simulation diagram of a seven level current source inverter with multi carrier modulation PWM technique. The voltage and current wave forms are shown in Fig. 12b.

Fig. 11(a-b): (a) Seven level circuit with pulse generator using PSIM and (b) Output current and voltage waveform

The harmonics having lower order frequency is reduced due to the modulation method preferred which is clearly shown in the current and voltage waveforms of the proposed converter.

Table 4 gives the Total harmonic distortion (THD) for different control strategies of the seven level paralleled converters. Current and Voltage THD values are nearly equal in the Traditional multicarrier modulation PWM, POD multicarrier modulation PWM and bipolar carrier overlapping PWM. Converter with APOD MCM, PDMCM, UCOPWM and USHPWM has higher harmonics. Most of the papers in the literature describe the working of multilevel inverter with reduced switches in order to reduce the control complexities. Simulation Analysis of total harmonic distortion of the seven level reduced switch multi-level current source inverter results clearly shows that

Fig. 12(a-b): (a) Traditional seven level circuit with MCM and (b) Output current and voltage waveform

converter harmonics level can be reduced based on the control technique employed for the operation of the multilevel inverters. For the topology proposed in this study Traditional MCM PWM and BCO PWM gives better results. If the system is chosen other than the proposed topology then any one of the remaining PWM techniques may give better result. When the level of the inverter is increased the resultant performance of the converter will be better in terms of harmonic reduction.

Table 4: Output current THD and voltage THD for various PWM control methods

| Control strategies | Current THD (%) | Voltage THD (%) |

|--------------------|-----------------|-----------------|

| Traditional MCM    | 15.23           | 12.61           |

| APOD MCM           | 20.11           | 17.95           |

| PD MCM             | 25.03           | 22.61           |

| POD MCM            | 15.16           | 12.60           |

| UCOPWM             | 21.00           | 19.44           |

| USHPWM             | 18.54           | 16.67           |

| BCOPWM             | 14.59           | 12.44           |

### CONCLUSION

Multi level converters are grown physically to a well-developed and fascinating solution for high-power with medium voltage applications from being an emerging technology. Initially, the improved power quality with higher power rating has become the major impulse and initiative for the development as well as research in multilevel converters. Anyway, the successive growth of technical methods and the development in applications like industry need will open fresh difficult and stimulating task also opportunities which trigger further improvements to multilevel converter technology.

In this study a different seven level paralleled converter is analysed with various PWM control methods using PSIM and MATLAB. The converter analysed in this work is best suitable for to be extrapolated in to higher levels by just adding two more switches with one inductor. In this work harmonic analysis of various control techniques were taken as the parameter to verify the effectiveness of control strategies. The simulation result shows that the both current THD and voltage THD for the bipolar carrier overlapping PWM strategy is less compared to the remaining PWM control methods examined. THD of the analysed converter can be further reduced by incorporating more number of levels in the converter.

### REFERENCES

Arthishri, K., R. Balasubramanian, P. Kathirvelu, S.P. Simon and R. Amirtharajan, 2014. Maximum power point tracking of photovoltaic generation system using artificial neural network with improved tracking factor. J. Applied Sci., 14: 1858-1864.

Balasubramanian, R., P. Kathirvelu, Shashwat and S. Palani, 2014a. Synchronous rotating reference frame based control technique for three-phase hybrid active power filter: A simulink approach. J. Applied Sci., 14: 1557-1563.

Balasubramanian, R., K.P. Karthirvelu, N. Divya, R. Amirtharajan and S. Palani, 2014b. Fuzzy controller based switched boost converter with reduced harmonics for micro grid application. J. Applied Sci., 14: 1928-1935.

Bashi, S.M., N. Mariun, N.F. Mailah and S. Alhalali, 2008. Low harmonics single phase multilevel power inverter. Asian J. Sci. Res., 1: 274-280.

Boost, M.A. and P.D. Ziogas, 1988. State-of-the-art carrier PWM techniques: A critical evaluation. IEEE Trans. Ind. Appl., 24: 271-280.

Chen, G., Z. Wu, Y. Zhu and J. Zhao, 2013. Simulation and analysis of random switching frequency space vector pulse width modulation. Inform. Technol. J., 12: 2009-2015.

Farahani, H., 2008. Investigation of modulation index, operational mode and load type on the SHEM current source inverter. J. Applied Sci., 8: 4376-4382.

# Res. J. Inform. Technol., 6 (3): 166-177, 2014

- Gholami, S. and A.R. Seifi, 2012. Mathematical analysis on pulse width modulated switching functions of matrix converter. Trends Applied Sci. Res., 7: 706-723.

- He, G., M. Wang, J. Gan and C. Liang, 2014. A new sector positioning method of the svpwm reference voltage space vector. Inform. Technol. J., 13: 927-933.

- Kathirvelu, K.P., R. Balasubramanian, O. Apurna and R. Amritharajan, 2014. Fuzzy logic controller based power conversion system fed from fuel cell. J. Applied Sci., 14: 1736-1742.

- Lai, J.S. and F.Z. Peng, 1996. Multilevel converters-a new breed of power converters. IEEE Trans. Ind. Appl., 32: 509-517.

- Mailah, N.F., S.M. Bashi, N. Mariun and I. Aris, 2008. Simulation of a three-phase multilevel unified power flow controller UPFC. J. Applied Sci., 8: 503-509.

- McGrath, B.P. and D.G. Holmes, 2002. Multicarrier PWM strategies for multilevel inverters. IEEE Trans. Ind. Electron., 49: 858-867.

- Ramezani, B., 2010. Speed control simulation for induction motor by multi level VSI-Fed to analyse current harmonics and selective harmonics elimination. J. Applied Sci., 10: 688-693.

- Vazquez, N., H. Lopez, C. Hernandez, E. Vaszaquez, R. Osorio and J. Arau, 2010. A different multilevel current-source inverter. IEEE Trans. Ind. Appl., 57: 2623-2631.

- Wu, W., J.G. Jiang and H. Liu, 2013. General optimization algorithm for capacitor voltage balance of multilevel inverters. Inf. Technol. J., 12: 2382-2389.